Intel Developer Forum Fall 2004: Day 1 Keynote

by Derek Wilson on September 7, 2004 5:11 PM EST- Posted in

- Trade Shows

What's New From the Keynote

Digital Home

Streaming DTCP/IP video

In the digital home arena, one of the cornerstones of encouraging pervasive sharing of digital media is security. To this end, we have been hearing about Intel's DTCP/IP (Digital Transmission Content Protection over IP). This time around, Intel was able to demonstrate this technology delivering movies using RealNetworks streaming media. Part of the demonstration involved running two streaming movies using DTCP/IP on one computer (on two different televisions). Intel also stated that Microsoft would officially be supporting DTCP/IP in an upcoming version of Windows Media Center Edition. While we are always cautious about the privacy and fair use concerns that could come up with such content protection schemes, we absolutely hope that this will end up becoming an unobtrusive content protection scheme that will do nothing but encourage content providers to move to digital delivery systems.

iAMT for Manageability

Intel didn't elaborate a great deal on this topic. Apparently, iAMT (active management technology) is going to try to move management tasks into Silicon. Though very vague, we got the impression that iAMT would focus on identifying different types of problems and taking some kind of automated action to correct issues. Cutting down time a technician needs to deal with relatively simple problems could significantly help companies save money on computer support costs. We will try to find out more about iAMT if we can this week.

Back to the Future: Cache and Parallelism

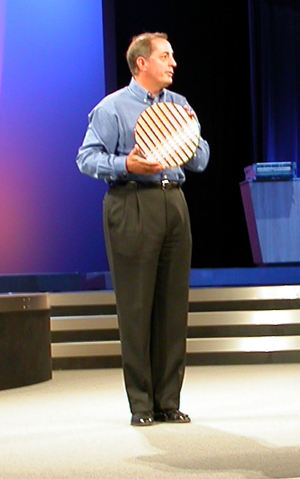

cache fabbed on 65nm process technology

Its not surprising that with the shift of focus away from megahertz and toward parallelism, cache technology would gain more and more focus. If Intel is really going to start pushing multithreaded applications and parallel computer, lager cache sizes will be necessary to compensate for the increased number of processes that will want to have data stored on chip. As an extension of the EE line, it has seemed obvious that Intel would be brining a 2MB cache version of prescott P4s to the end user. Intel, today, confirmed the future of a 2MB cache P4, referred to as a Pentium 4 with a "performance oriented SKU." Much time was also spent talking about the Centrino line and other various technologies that incorporate higher parallelism. The most interesting of which was a demo of their dual core Itanium processor.

28 Comments

View All Comments

Lonyo - Wednesday, September 8, 2004 - link

We knew that they woul dhave 24MB of cache a while ago.There was a post on the Anandtech forums asking why you would need such a large amount of cache.

kherman - Wednesday, September 8, 2004 - link

So, am I the only one that noticed that EACH PROCESOR HAS 24 MEG OF CACHE ON IT!First image on page 3:

http://www.anandtech.com/tradeshows/showdoc.aspx?i...

ysrgrathe - Wednesday, September 8, 2004 - link

iCube is supposed to be presenting their NMP-5000A network media player at the IDF. They won an award last year for their NMP-4000 model, which has also received a lot of positive reviews. I'm interested to know more; iCube has nothing on their site other than a press release about the IDF presentation an a picture showing dual antennas.From last year's timeline I would expect the product to launch around Christmas; would be nice to have some info before then. Anyone at the convention hear anything?

JarredWalton - Wednesday, September 8, 2004 - link

^^^ This is why you shouldn't do drugs, kids.AMDjihad - Wednesday, September 8, 2004 - link

AHAHAH> INtel loses like a faceusut. AHAHA. Whorlovas. Intel loses. I agrre witgb alkb of you. Intel sucks. HAHAHA> OPertin ins bwext at everythoing. Hah wether simulation.s I can do that. HAhahha.TrogdorJW - Wednesday, September 8, 2004 - link

#12 - Itanium 2 can issue up to 8 instructions per clock, but stalls on one set of instructions can still occur. If you have hyper-threading, you have more potential to fill all of the available issue slots. That's why the POWER5 chip from IBM also has a version of hyperthreading, although I believe IBM calls it "symmetric multi-threading" (SMT). Oh, and Itanium also has more FP/SSE execution units than the P4/Xeon, which is why it has such "kick booty FP".#8 - That really didn't make much sense, partly due to the incorrect use of the Enter key. But let's address this: "Intel has not had a demonstrable lead in design or manufacturing in several years. They have only been maintaining parity with the competition. They intially argued against the need for .13 micron and smaller die shrink, they followed the lead of IBM and AMD. And followed again when copper replaced aluminum in the CPU." Ugh, where to begin...

Okay, let's make this clear. Intel has never argued against .13 micron or any other process shrinks. They have said at times that it was not necessary *YET*, and that they would pursue it in the future. This happened with copper interconnects (AMD used them in .18 micron while Intel waited until late in their .13 micron use), and it happened with x86-64. Don't confuse "we aren't doing that yet" with "we aren't pursuing that *ever*".

You can make a case for some issues with their designs of late, but as far as technology? We've seen 90 nm parts from Intel for almost a year now (more if you count early samples), while AMD is only just starting to ship them. IBM went with SOI first and Intel went with strained silicon. They're both pushing the process technology in different ways. To say Intel hasn't been perfect is absolutely valid, but to say they're failing completely (which seems to be the gist of your post) is taking it way too far.

Just my opinion here, of course.

mkruer - Tuesday, September 7, 2004 - link

The only advantade that the Itanic has in computer operations is that is has a kick booty FP operation. problem is that most progrmas use limited floating point. on top of that I would not be to supprised to see the FP core migrating into the Xeon, or what ever intel is going to call their next gen chipsprockkets - Tuesday, September 7, 2004 - link

Big deal, 1.7 billion transistors, probably 95% of that is just cache memory.Again, why would Itaniums need Hyperthreading? If your EPIC code alreay is made to process so many instructions at once in parallel, then how is hypthreading going to make any difference?

ksherman - Tuesday, September 7, 2004 - link

sorry, my post was intended for #8 not #9ksherman - Tuesday, September 7, 2004 - link

^ half that didnt make sense...and I am sure that 4 dual core opterons could probably do real time weather simulations too, its not an Intel exclusive capability...