The AMD 3rd Gen Ryzen Deep Dive Review: 3700X and 3900X Raising The Bar

by Andrei Frumusanu & Gavin Bonshor on July 7, 2019 9:00 AM ESTSection by Dr. Ian Cutress (Orignal article)

Windows Optimizations

One of the key points that have been a pain in the side of non-Intel processors using Windows has been the optimizations and scheduler arrangements in the operating system. We’ve seen in the past how Windows has not been kind to non-Intel microarchitecture layouts, such as AMD’s previous module design in Bulldozer, the Qualcomm hybrid CPU strategy with Windows on Snapdragon, and more recently with multi-die arrangements on Threadripper that introduce different memory latency domains into consumer computing.

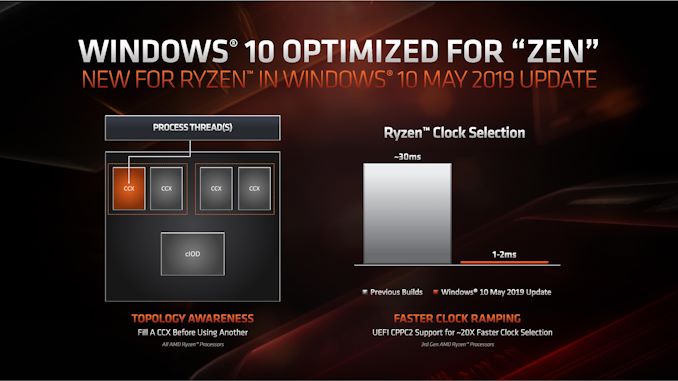

Obviously AMD has a close relationship with Microsoft when it comes down to identifying a non-regular core topology with a processor, and the two companies work towards ensuring that thread and memory assignments, absent of program driven direction, attempt to make the most out of the system. With the May 10th update to Windows, some additional features have been put in place to get the most out of the upcoming Zen 2 microarchitecture and Ryzen 3000 silicon layouts.

The optimizations come on two fronts, both of which are reasonably easy to explain.

Thread Grouping

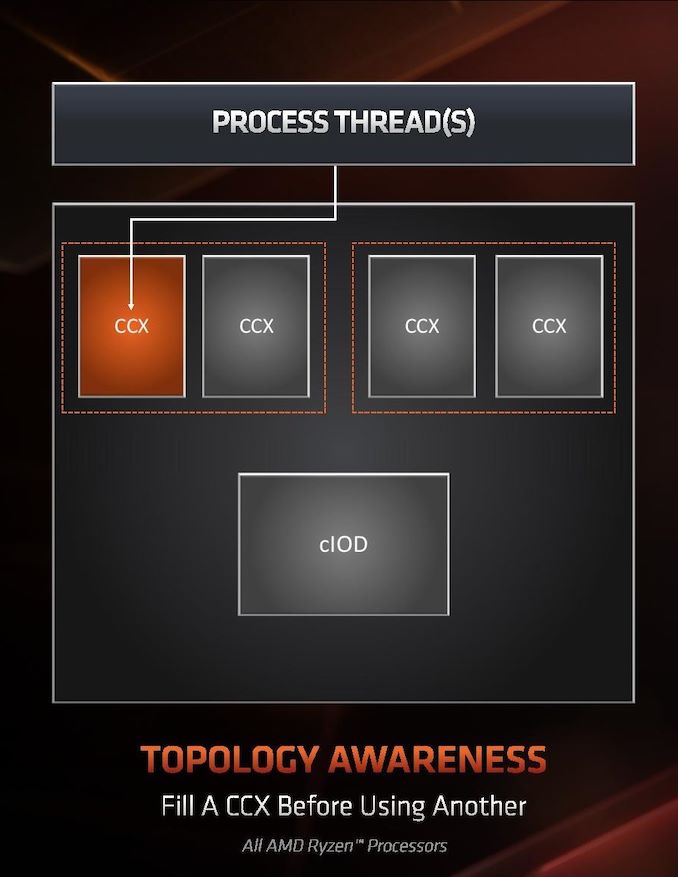

The first is thread allocation. When a processor has different ‘groups’ of CPU cores, there are different ways in which threads are allocated, all of which have pros and cons. The two extremes for thread allocation come down to thread grouping and thread expansion.

Thread grouping is where as new threads are spawned, they will be allocated onto cores directly next to cores that already have threads. This keeps the threads close together, for thread-to-thread communication, however it can create regions of high power density, especially when there are many cores on the processor but only a couple are active.

Thread expansion is where cores are placed as far away from each other as possible. In AMD’s case, this would mean a second thread spawning on a different chiplet, or a different core complex/CCX, as far away as possible. This allows the CPU to maintain high performance by not having regions of high power density, typically providing the best turbo performance across multiple threads.

The danger of thread expansion is when a program spawns two threads that end up on different sides of the CPU. In Threadripper, this could even mean that the second thread was on a part of the CPU that had a long memory latency, causing an imbalance in the potential performance between the two threads, even though the cores those threads were on would have been at the higher turbo frequency.

Because of how modern software, and in particular video games, are now spawning multiple threads rather than relying on a single thread, and those threads need to talk to each other, AMD is moving from a hybrid thread expansion technique to a thread grouping technique. This means that one CCX will fill up with threads before another CCX is even accessed. AMD believes that despite the potential for high power density within a chiplet, while the other might be inactive, is still worth it for overall performance.

For Matisse, this should afford a nice improvement for limited thread scenarios, and on the face of the technology, gaming. It will be interesting to see how much of an affect this has on the upcoming EPYC Rome CPUs or future Threadripper designs. The single benchmark AMD provided in its explanation was Rocket League at 1080p Low, which reported a +15% frame rate gain.

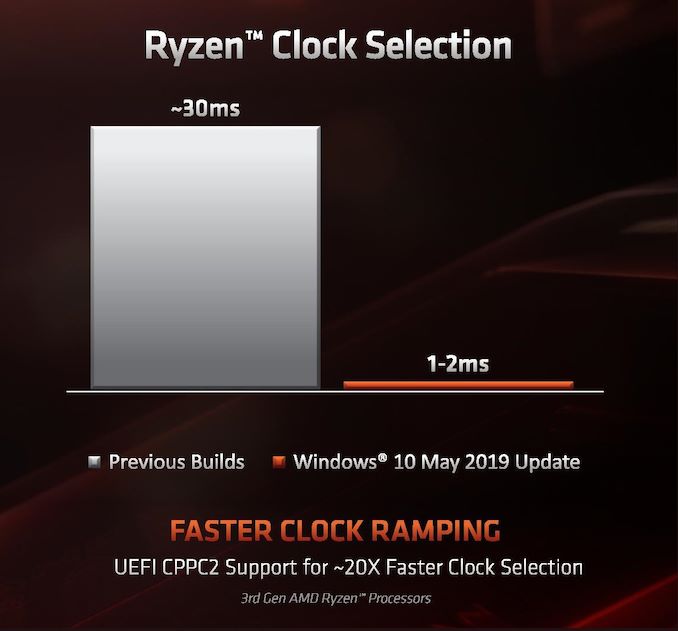

Clock Ramping

For any of our users familiar with our Skylake microarchitecture deep dive, you may remember that Intel introduced a new feature called Speed Shift that enabled the processor to adjust between different P-states more freely, as well as ramping from idle to load very quickly – from 100 ms to 40ms in the first version in Skylake, then down to 15 ms with Kaby Lake. It did this by handing P-state control back from the OS to the processor, which reacted based on instruction throughput and request. With Zen 2, AMD is now enabling the same feature.

AMD already has sufficiently more granularity in its frequency adjustments over Intel, allowing for 25 MHz differences rather than 100 MHz differences, however enabling a faster ramp-to-load frequency jump is going to help AMD when it comes to very burst-driven workloads, such as WebXPRT (Intel’s favorite for this sort of demonstration). According to AMD, the way that this has been implemented with Zen 2 will require BIOS updates as well as moving to the Windows May 10th update, but it will reduce frequency ramping from ~30 milliseconds on Zen to ~1-2 milliseconds on Zen 2. It should be noted that this is much faster than the numbers Intel tends to provide.

The technical name for AMD’s implementation involves CPPC2, or Collaborative Power Performance Control 2, and AMD’s metrics state that this can increase burst workloads and also application loading. AMD cites a +6% performance gain in application launch times using PCMark10’s app launch sub-test.

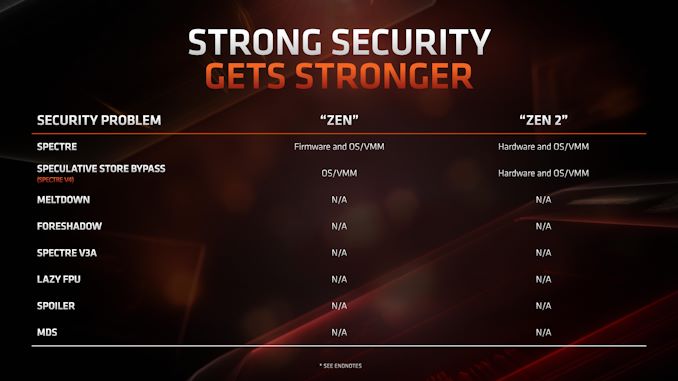

Hardened Security for Zen 2

Another aspect to Zen 2 is AMD’s approach to heightened security requirements of modern processors. As has been reported, a good number of the recent array of side channel exploits do not affect AMD processors, primarily because of how AMD manages its TLB buffers that have always required additional security checks before most of this became an issue. Nonetheless, for the issues to which AMD is vulnerable, it has implemented a full hardware-based security platform for them.

The change here comes for the Speculative Store Bypass, known as Spectre v4, which AMD now has additional hardware to work in conjunction with the OS or virtual memory managers such as hypervisors in order to control. AMD doesn’t expect any performance change from these updates. Newer issues such as Foreshadow and Zombieload do not affect AMD processors.

447 Comments

View All Comments

John_M - Sunday, July 7, 2019 - link

Yes. The integrated memory controller is on the IO die, which is part of the Ryzen SoC, not the chipset.BushLin - Monday, July 8, 2019 - link

Right now, there's no indication what CL / timings are applied to all the other systems. CL16 is indeed bottom of the barrel for DDR-3200, you would hope there's no shenanigans with Intel getting CL12 DDR-2666. Why not just run all the systems with the same DDR-3200, it's not like they can't do it.profiaudi - Wednesday, July 10, 2019 - link

Not to be too rude, but the IMC is on the io chipLet, not the chipSet. The chipset actually has an important role for the memory speed, in that a chipset defines a platform and a platform imposes requirements on the power supply and trace routing. While the IMC in 3rd gen can handle 3200MT/s+ completely fine, it is guaranteed to do so only one X570. Anything older is a dice roll as the boards were not designed for such speeds (not a requirement for the older platform).waja - Tuesday, July 23, 2019 - link

Do you know george stevenson story?He earn 3657$ every month at home just working few hours on internet see more by open this connection and click home button.FOR MORE INFORMATION COPY THIS SITE.......... www.online-3.comAndrei Frumusanu - Sunday, July 7, 2019 - link

Just as note for those who haven’t been following: This review wasn’t written by our usual resident CPU editor, Dr Ian Cutress as he unfortunately the timing didn’t work out. We only had a few days time with the new Ryzen CPUs, as such, you might noticed a few bits and pieces missing in our article that we’ll try to address in the next hours and days. We’ll be trying to update the piece with more information and data as soon as we can. Thanks.Also huge thanks to Gavin Bonshor who actually did all the testing and collected all the data for this review, thumb up to him.

plonk420 - Sunday, July 7, 2019 - link

hoping a speedy recovery for him! loved his video with Wendell!loving the article, too. don't suppose you could test cross-CCX latency?

plonk420 - Sunday, July 7, 2019 - link

e.g. pcper.com/2017/06/the-intel-core-i9-7900x-10-core-skylake-x-processor-review/3/main interest is if it is low enough to be harnessed by RPCS3 (PS3 emulator)

ballsystemlord - Sunday, July 7, 2019 - link

CCX benchmarks would be nice.IF power benchmarks were also done last time and probably in the works.

shakazulu667 - Sunday, July 7, 2019 - link

Are Intel results with or without spectre et al mitigations?Ryan Smith - Sunday, July 7, 2019 - link

They are with Spectre and Meltdown mitigations. They are not new enough results to include anything for Fallout/ZombieLoad.