AMD Zen 2 Microarchitecture Analysis: Ryzen 3000 and EPYC Rome

by Dr. Ian Cutress on June 10, 2019 7:22 PM EST- Posted in

- CPUs

- AMD

- Ryzen

- EPYC

- Infinity Fabric

- PCIe 4.0

- Zen 2

- Rome

- Ryzen 3000

- Ryzen 3rd Gen

New Instructions

Cache and Memory Bandwidth QoS Control

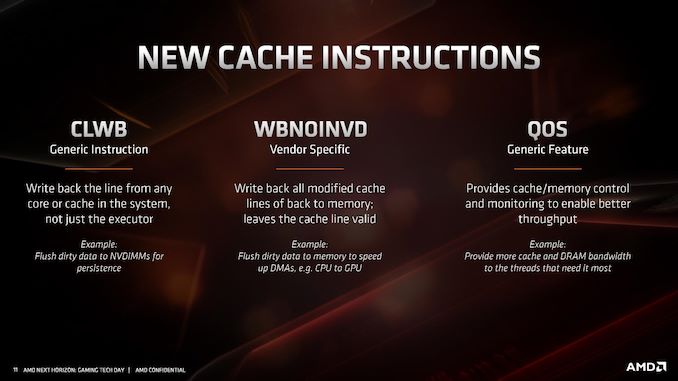

As with most new x86 microarchitectures, there is a drive to increase performance through new instructions, but also try for parity between different vendors in what instructions are supported. For Zen 2, while AMD is not catering to some of the more exotic instruction sets that Intel might do, it is adding in new instructions in three different areas.

The first one, CLWB, has been seen before from Intel processors in relation to non-volatile memory. This instruction allows the program to push data back into the non-volatile memory, just in case the system receives a halting command and data might be lost. There are other instructions associated with securing data to non-volatile memory systems, although this wasn’t explicitly commented on by AMD. It could be an indication that AMD is looking to better support non-volatile memory hardware and structures in future designs, particularly in its EPYC processors.

The second cache instruction, WBNOINVD, is an AMD-only command, but builds on other similar commands such as WBINVD. This command is designed to predict when particular parts of the cache might be needed in the future, and clears them up ready in order to accelerate future calculations. In the event that the cache line needed isn’t ready, a flush command would be processed in advance of the needed operation, increasing latency – by running a cache line flush in advance while the latency-critical instruction is still coming down the pipe helps accelerate its ultimate execution.

The final set of instructions, filed under QoS, actually relates to how cache and memory priorities are assigned.

When a cloud CPU is split into different containers or VMs for different customers, the level of performance is not always consistent as performance could be limited based on what another VM is doing on the system. This is known as the ‘noisy neighbor’ issue: if someone else is eating all the core-to-memory bandwidth, or L3 cache, it can be very difficult for another VM on the system to have access to what it needs. As a result of that noisy neighbor, the other VM will have a highly variable latency on how it can process its workload. Alternatively, if a mission critical VM is on a system and another VM keeps asking for resources, the mission critical one might end up missing its targets as it doesn’t have all the resources it needs access to.

Dealing with noisy neighbors, beyond ensuring full access to the hardware as a single user, is difficult. Most cloud providers and operations won’t even tell you if you have any neighbors, and in the event of live VM migration, those neighbors might change very frequently, so there is no guarantee of sustained performance at any time. This is where a set of dedicated QoS (Quality of Service) instructions come in.

As with Intel’s implementation, when a series of VMs is allocated onto a system on top of a hypervisor, the hypervisor can control how much memory bandwidth and cache that each VM has access to. If a mission critical 8-core VM requires access to 64 MB of L3 and at least 30 GB/s of memory bandwidth, the hypervisor can control that the priority VM will always have access to that amount, and either eliminate it entirely from the pool for other VMs, or intelligently restrict the requirements as the mission critical VM bursts into full access.

Intel only enables this feature on its Xeon Scalable processors, however AMD will enable it up and down its Zen 2 processor family range, for consumers and enterprise users.

The immediate issue I had with this feature is on the consumer side. Imagine if a video game demands access to all the cache and all the memory bandwidth, while some streaming software would get access to none – it could cause havoc on the system. AMD explained that while technically individual programs can request a certain level of QoS, however it will be up to the OS or the hypervisor to control if those requests are both valid and suitable. They see this feature more as an enterprise feature used when hypervisors are in play, rather than bare metal installations on consumer systems.

216 Comments

View All Comments

GreenReaper - Tuesday, June 11, 2019 - link

A lot of progress has been made. Browsers are far more multithreaded than they once were - and as web pages become more complex, that benefit can scale. Similarly, databases and rendering can scale very well over certain operations.Said scaling tends to work best for the longest operations, because they can be split up into chunks without too much overhead. The overall impact should be that there are fewer long, noticeable delays. There isn't so much progress for things that are already pretty fast - or long sequences of operations that rely on one another. (However, precomputing and prefetching can help.)

stephenbrooks - Thursday, June 13, 2019 - link

I find it surprising how they add these smallish increases onto execution width, out of order buffers, register files etc. The IPC hasn't stopped increasing, it's just slow-ish. Maybe they're fighting power and latency in those part of the core so the 2x density from a node doesn't translate fully.Santoval - Tuesday, June 11, 2019 - link

Prices should drop when the competition with Intel becomes fiercer. I don't expect that anytime soon though.. It doesn't look like Intel will manage to release Ice Lake CPUs (except apparently the -U and -Y ones they announced) this year or at all.Their 10nm+ node is still having serious issues with clocks and thermals, and the yields are much lower than TSMC's 7nm (high performance) node. So "word on the street" is that they won't release Ice Lake CPUs for desktop at all. Id est that they'll can them and release instead Tiger Lake desktop CPUs fabbed with their fixed (??) 10nm++ node variant late next year (as in Q4 2020).

piroroadkill - Wednesday, June 12, 2019 - link

You're wrong. You get more performance than Intel at a lower price. In the case of the 3950X, it's significant. To sell them cheaper would devalue an incredible product, for no reason.Targon - Thursday, June 13, 2019 - link

Ryzen 7 2700X vs. Ryzen 7 3700X. Same price, better performance. Looking at the 3800X which is $399, look at the IPC+clock speed improvements. The 3900X will obviously come at a cost, because you are getting 50% more cores for that increased price. Single threaded though....at what point do you really focus on how fast or slow a single threaded program is running in this day and age where you run dozens of processes at the same time? If you are running dozens of single threaded programs, then performance will change based on how the OS scheduler assigns them to different CPU cores.Qasar - Thursday, June 13, 2019 - link

jjj" They give us around 20% ST gains (IPC+clocks) but at a cost. " that same thing could be said about intels cpus over the last few years... how much performance increase did they give us year over year ?? all while only giving is 4 cores for the mainstream... amd's prices are just fine.. intel is the one that should be dropping their prices, some as low as the $50 you say, but most, $500 or more

Tunnah - Monday, June 10, 2019 - link

I bet now Intel is just going to completely flood ads with the title "Intel beats AMD in pure FPS tests!", because they'll get 210fps where AMD gets 200. And some people will eat it up.I'm so excited for this upgrade. Replacing a 2700K with a 3800X, where I'll not only get a doubling of cores, but clock for clock I reckon it's a 40, 50% improvement there too.

My Civ games are gonna be so zoomy now..

xrror - Monday, June 10, 2019 - link

Intel will always beat AMD ......

...

(at a price point you don't give a f*ck about) (4 digits or more)

Are you a micro-trader hardwired into the BS Stock Exchange? You think $1000+ is too much for the fully enabled processor arch you want to overclock should cost you?

Sorry, Intel doesn't have the time of day for you after 2011, after Sandy Bridge took away the ability to overclock blessed "K" skus...

oh sure, there are others. IDT and Cyrix are dead but... let me introduce you to...

AMD

xrror - Monday, June 10, 2019 - link

This isn't aimed at you Tunnah. I meant it as humor.Read my comment like some exciting infocommercial, with ... (insert commanding infomercial voice here) hehe

Makaveli - Tuesday, June 11, 2019 - link

The 2700k and the 3800X are both 8C 16T designs.