Examining Intel's Ice Lake Processors: Taking a Bite of the Sunny Cove Microarchitecture

by Dr. Ian Cutress on July 30, 2019 9:30 AM EST- Posted in

- CPUs

- Intel

- 10nm

- Microarchitecture

- Ice Lake

- Project Athena

- Sunny Cove

- Gen11

Thunderbolt 3: Now on the CPU*

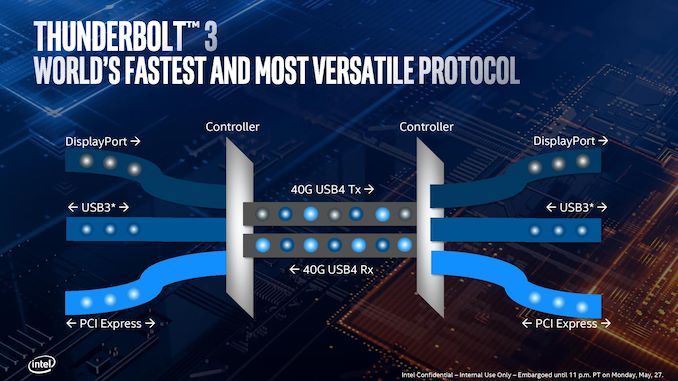

One of the big failures of the Thunderbolt technology since its inception has been its adoption beyond that Apple ecosystem. In order to use it, both the host and the device needed TB controllers supplied by Intel. It wasn’t until Thunderbolt 3 started to use USB Type-C, and Thunderbolt 3 having enough bandwidth to support external graphics solutions, that we started to see the number of available devices start to pick up. The issue still remains that the host and device need an expensive Intel-only controller, but the ecosystem was starting to become more receptive to its uses.

With Ice Lake, that gets another step easier.

Rather than bundle TB3 support into the chipset, Intel has integrated it on the die of Ice Lake, and it takes up a sizable amount of space. Each Ice Lake CPU can support up to four TB3 ports, with each TB3 port getting a full PCIe 3.0 x4 root complex link internally for full bandwidth. (For those keeping count, it means Ice Lake technically has 32 PCIe 3.0 lanes total).

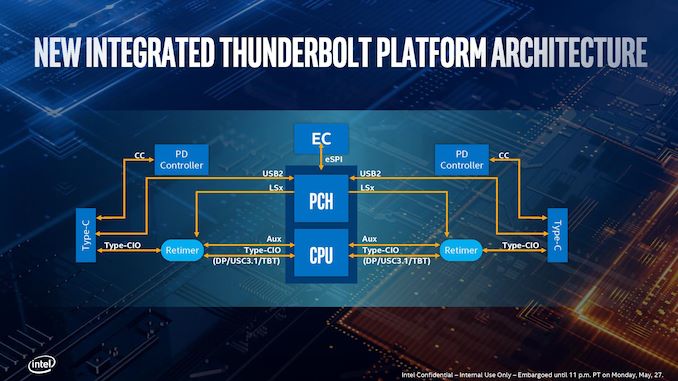

Intel has made it so each side of the CPU can support two TB3 links direct from the processor. There is still some communication back and forth with the chipset (PCH), as the Type-C ports need to have USB modes implemented. It’s worth noting that TB3 can’t be directly used out of the box, however.

Out of the four ports, it will be highly OEM dependent on how many of those will actually make it into the designs – it’s not as simple as just having the CPU in the system, but other chips (redrivers) are needed to support the USB Type-C connector. Power delivery too requires extra circuitry, which costs money. So while Intel advertises TB3 support on Ice Lake, it still needs something extra from the OEMs. Intel states that a retimer for the integrated solution is only half the size compared to the ones needed with the TB3 external chips, as well as supporting two TB3 ports per retimer, therefore halving the number of retimers needed.

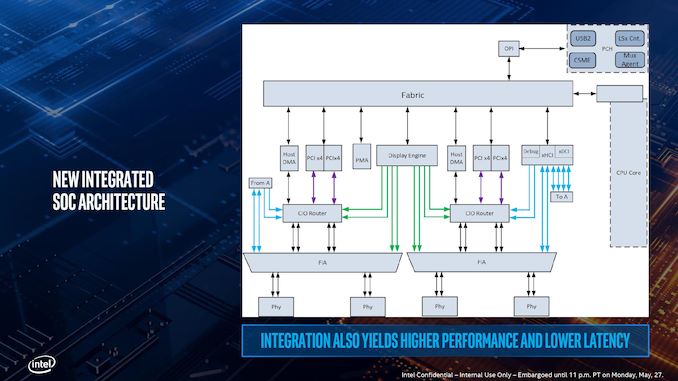

Here’s a more detailed schematic, showing the complexities of adding in TB3 into a chip, with the four PCIe x4 complexes shown moving out to each of the individual PHYs at the bottom, and connected back into the main SoC interconnect fabric. The display engine also has to control what mode the TB3 ports are in, and what signals are being sent. Wake up times for TB3 in this fashion, according to Intel, are actually slightly longer compared to a controller implementation, because the SoC is so tightly integrated. This sounds somewhat counterintuitive, given that the requisite hardware blocks are now closer together, but it all comes down to power domains – in a separate chip design, each segment has a separate domain with individual power up/down states. In an integrated SoC, Intel has unified the power domains to reduce complexity and die area, which means that more careful management is required but latency ultimately increases a little bit.

The other upside to the tightly coupled integration is that Intel stated that this method of TB3 is a lot more power efficient that current external chip implementations. However they wouldn’t comment on the exact power draw of the TB3 block on the chip as it corresponds to the full TDP of the design, especially in relation to localized thermal density (Intel was initially very confused by my question on this, ultimately saying that the power per bit was lower compared to the external chip, so overall system power was lower – they seemed more interested in discussing system power over chip power). Intel did state that the difference between an idle and a fully used link was 300 mW, which suggests that if all four links are in play, we’re looking at 1.2 W. When asked, Intel stated that there are three different power delivery domains within the TB3 block depending on the logic, that the system uses integrated voltage regulation, and the TB3 region has an internal power rail that is shared with some of the internal logic of the CPU. This has implications when it comes to time-to-wake and idle power, but Intel believes it has found a good balance.

Regarding USB4 support, Intel stated that it is in the design, and they are USB4 compliant at this point, but there might be changes and/or bugs which stop it from being completely certified further down the line. Intel said that it ultimately comes down to the device side of the specification, although they have put as much in as they were able given the time constraints of the design. They hope to be certified, but it’s not a guarantee yet.

Depending on who you speak to, this isn’t Intel’s first crack at putting TB3 into CPU silicon: the chip that Intel never wants to talk about, Cannon Lake, supposedly also had an early TB3 design built inside that never worked. But Intel is confident in its Ice Lake implementation, especially with supporting four ports. I wouldn’t be surprised if this comes to desktop when Intel releases its first generation 10nm desktop processors.

*The asterisk in the title of this page is because you still need external hardware in order to enable TB3.

107 Comments

View All Comments

notashill - Tuesday, July 30, 2019 - link

Are those RAM/SSD targets really "greater than" 8GB/256GB or is it supposed to be "greater than or equal to"?Either way I would love to see an end to companies having >$1000 machines with pathetically low RAM/storage and then charging 500%+ markups to upgrade them to something decent. Like Microsoft's $1200 to go from 4/128 to 16/512.

mkozakewich - Wednesday, July 31, 2019 - link

I can't believe Microsoft has been using 4 GB as their base amount for the last six years. At some point it becomes insulting.repoman27 - Tuesday, July 30, 2019 - link

“Intel uses the ‘U’ designation for anything from 9W to 28W TDP, which covers all the mobile ultra-premium devices.”No they don’t. 9W are Y Series, 15 and 28W are U Series. This is all clearly stated in Intel’s publicly available product briefs for 10th Generation Core processors.

HStewart - Tuesday, July 30, 2019 - link

I be curious for more information on the Y processors - what the performance difference between Y and U. But it looks like these Ice Lake chips are designed for Ultraportable machines and not designed to replace to higher end ones - even like my Dell XPS 15 2in1 - I am really curious about that replacement - it's GPU is probably short lived possibly in updated higher voltage Ice Lake with Gen 11 graphics or new version with Xe graphics. I also have a Dell XPS 13 2in1 with Y processor - I am actually bringing it to meeting today - it is lightweight and does not really need that much power for what I using it for. I think it will be very interesting to compare this new XPS 13 2in1 and the existing XPS 15 2in1 - yes 15 2in1 has faster processor - but it not Ice Lake and that could make a huge difference.Hixbot - Tuesday, July 30, 2019 - link

4.2% annual IPC growth doesn't sound great but it is better than anything we've seen since SandyBridge.Targon - Tuesday, July 30, 2019 - link

And that should make people question the claims about performance increases. Mind you, how much performance has been lost on Intel chips due to the security issues? Intel may be comparing theoretical performance increases, without disclosing the fact that first through 9th generation have actually lost performance since launch due to security mitigations.So, +18% IPC, but -20% due to security mitigations for issues that are still there. Has Intel actually fixed the problems with the memory controller and other problems that allow for Meltdown and the other problems, rather than mitigating around the problem? If a problem has existed since first generation Core processors that turns out to be a design flaw, that also shows that the fundamental core design hasn't changed all THAT much.

rahvin - Wednesday, July 31, 2019 - link

Meltdown and some of the first spectre mitigations are going to be fixed in the hardware. Later spectre variants are probably only fixed in microcode and software.Where that line is drawn is going to be determined by when they froze the physical design for tapeout.

eek2121 - Wednesday, July 31, 2019 - link

I'm not knocking Intel on the IPC growth. If they had an 18% increase, great for them! However, mobile Intel CPUs of any variant (U, HK, Y, etc.) are much slower than their desktop counterparts. My Core i7 2600k absolutely destroys the 6700HK in my laptop. Laptops in general are designed to be low power devices, so performance is never the number one factor in designing a laptop, even on the high end. The only exception to this is the so called 'desktop replacements' that weigh a ton, have desktop class hardware, and basically need to be plugged in to not have the battery die after an hour.That's also the reason I take this announcement with a grain of salt. 18% on mobile is one thing. 18% on the desktop is something else. As I've mentioned to people here and elsewhere, the smaller the process, the harder it is to maintain high clock speeds. Also, from reading certain documentation, it seems that part of that 18% is counting the addition of AVX-512. I could be mistaken though.

erple2 - Wednesday, July 31, 2019 - link

Wow, really? That has not been my experience at all. My 6700hq has generally been (usually significantly) better performing than my 2600k for the vast majority of tasks I've thrown at it.jospoortvliet - Monday, August 5, 2019 - link

Any task that requires sustained compute will of course suffer on thr lower power budget on mobile. But tasks which require short bursts of activity will do better thanks to vastly improved turbo since the 2600k. So depending on what you do your impression might very well be accurate.