ChipRebel Releases Exynos 9820 Die Shot: M4 CPUs in New Cluster

by Andrei Frumusanu on March 9, 2019 3:30 AM EST- Posted in

- Smartphones

- Samsung

- Mobile

- SoCs

- ChipRebel

- Exynos 9820

Every time a new SoC comes one, the one thing we eagerly await is for someone to release a die shot of the new chip. This process is most interesting when the new chip either comes with a new microarchitecture or a new process node. Last November, we covered the release of ChipRebel’s Kirin 980 die shot which gave us the first ever look of Arm’s new Cortex A76 CPU as well as Mali G76 GPU on a new 7nm process node.

The folks over there are at it again and have seemingly been very busy overnight, this time around tearing down the Galaxy S10 with the new Exynos 9820. I’ve been going back and forth with the ChipRebel team on these last two projects and they’re great guys, definitely visit them if you are in need of die shots.

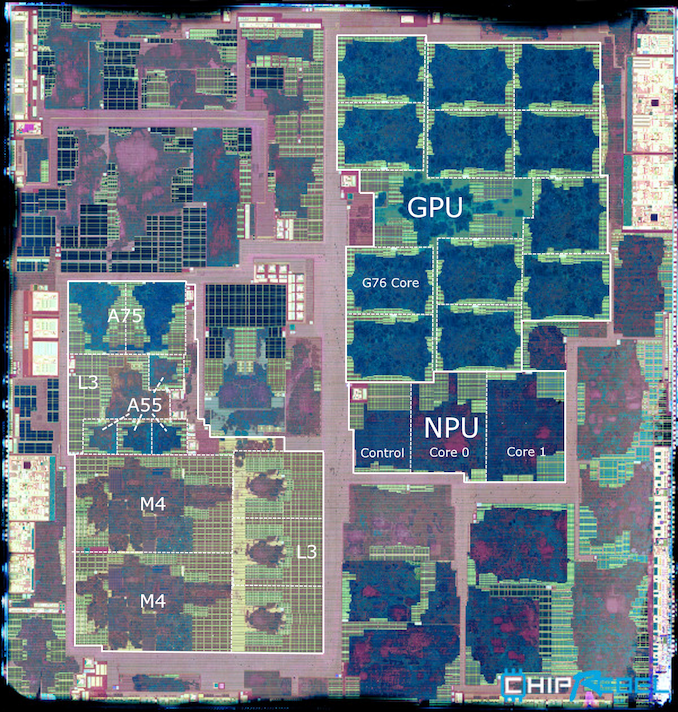

Die shot: Chip Rebel - Annotations/labelling: Andrei @ AnandTech

8nm not as small as 7nm

The first thing standing out for the Exynos 9820 is the fact that at ~127mm², the chip has actually grown compared to the 10LPP Exynos 9810 of last year. Samsung’s 8LPP node isn’t as aggressive in scaling as TSMC’s 7nm process, and in theory the process node should bring a conservative 15% reduced area compared to its preceding node, leaving TSMC at a notable density advantage this generation. Compared to the Kirin 980 at 74.13mm², the Snapdragon 855 at 73.27mm² and even Apple’s A12 at 83.27mm², the new Exynos 9820 clearly stands out as out of line compared to the competition.

The Exynos 9820 also changes a lot internally, compared to the Exynos 9810 last year. First off we notice that the CPU cluster isn’t as prominent as it was last year. The reason for this is simply that Samsung opted to only employ two of its new generation M4 cores as opposed to the quad-core layout of the M3 in the 9810.

Interesting in the die shot is the new cluster layout: Next to the M4 cores we see now three L3 slices with a similar design as we saw in the 9810. However north of the two M4 cores we see a further L3 slice that differs from the other three. This slice seems to be the one that connects the new Cortex A55 and A75 cores to Samsung’s cluster.

I’ve had the Galaxy S10+ with the Exynos 9820 in-house since yesterday, and I can confirm that the L3 cache has remained at a total of 4MB, although I need a bit more time to figure out exactly how much of this is accessible by the Cortex cores as there’s power management policies coming into play.

The important thing to note here is that the Cortex A55 cores are no longer handicapped by not sharing the same higher level cache hierarchy as the rest of the CPU complex.

The new Exynos M4 cores clock up to 2.73GHz, the A75 cores at up to 2.31GHz and the A55 cores up to 1.95GHz.

On the GPU side of things, we still see Samsung dedicate a lot of area to the Mali G76MP12 – although it’s doesn’t look as big as last year’s G72MP18.

Finally, below the GPU, we find Samsung’s new NPU. This is a dual-core design running at up to 933MHz and offering up to 1.9TOPs at 8-bit precision, although Samsung looks to be counting 6.9TOPs in quantised models. Samsung themselves publish the die area of this block to be 5.5mm².

We thank the guys at ChipRebel for sharing this die shot with the public as it offers great analysis of Samsung’s new chip! On our side, we have the S10+ in-house now and I’ll be working on the full detailed device+SoC review.

66 Comments

View All Comments

Death666Angel - Saturday, March 9, 2019 - link

The integration of two A75 seems to be a weird strike against the M4 already. Either the M4 is good enough to be the big core for A55 or it is not. Using 2 additional A75 seems like they went with "not" but couldn't just scrap it. I'm looking forward to Andrei's deep dive. :Dshadowx360 - Saturday, March 9, 2019 - link

Not necessarily. Likely a cost-saving measure since the M4 cores are so massive, and in last year's 4xM3 design, the cores could never hit maximum voltages simultaneously due to thermals. If they were worried about the performance of the M4 cores they could have gone with a 4xA76 setup. Even the M3 cores can probably outperform an A76 if the scheduler and thermals weren't so terrible.Death666Angel - Sunday, March 10, 2019 - link

Well, I'm more thinking about how it should be "BIG.little" and not "HUGE.Big.little". It's weird to have 3 tiers of CPU cores in a product like this, where everyone else has one or two, tops.And if I remember the older deep dive with fixed schedulers correctly, it caught up a bit to the Snapdragon then, but the SD was still faster and less power hungry. And if I remember the Exynos announcement article, I think Andrei said they would need to outperform their announced improvements to come close to this generations Snapdragon. And A76 has been shown to be a massively impressive core, so far. So I don't think you are necessarily correct.

phoenix_rizzen - Monday, March 11, 2019 - link

SD855 has 3 CPU clusters (1+3+4).MediaTek has had 3 CPU clusters for awhile (usually 2+4+4) now. I believe they were the first, although their implementations haven't been that great.

There's another one with 3 CPU clusters as well, but I can't think of it right now. Usually it's 2+2+4 to still give an 8-core CPU.

Unless you mean having 3 different types of CPU cores in a SoC, which doesn't appear to be prevalent in the industry (yet?).

twotwotwo - Saturday, March 9, 2019 - link

Yeah, the M4's had better be zippy. Three tiers is also interesting: is the workload varied enough that all three of them actually get a lot of use, and do all three types justify their cost?Also *geez* A55s are tiny. If I were designing an SoC I'd spam some more and say "hey, find ways to use threads and your stuff'll zoom." Probably a good reason I'm not designing SoCs, heh.

jeremyshaw - Sunday, March 10, 2019 - link

Having 8x small cores was a common thing in midrange phones for a while. However, the small in-order cores were just slow in single threaded tasks. Well, not "slow" slow, but not fast.twotwotwo - Sunday, March 10, 2019 - link

Yep, imagining still 1-2 large cores but a lot of small. And just random spitballing anyway, really.FunBunny2 - Monday, March 11, 2019 - link

"Having 8x small cores"multi-processor design remains front-of-mind for many, but butts up against the simple fact that they ain't many embarrassingly parallel problems in the real world. phone ain't one of em. and 'running' multiple apps at the same time per processor also ain't the same thing. esp. if the apps overwhelm the processor.

tuxRoller - Monday, March 11, 2019 - link

Just did a quick measurement and got M4 ~ 3.65 A75, while A75 ~ 3.45 A55Those ratios are interestingly close.

An A75 being, in general, somewhere between 2-3x faster than an A55 seems about right. So the 3.5x land grab seems pretty good especially since that accounts for the substantial transition to ooo.

OTOG, the M4 can issue and retire 50% (or twice the ints and 1.5 fp) ops than the A76. The GB scores should be close to ideal for keeping those units fed, and you see ~4200 vs 3800 & 3800 vs 3300.

Some of the subtests (histogram, aes, pdf) approach 1.5 but not many.

Dodozoid - Saturday, March 9, 2019 - link

Do you have the S10+ with snapdragon aswel or have you decided to source different snapdragon device?