Intel's Architecture Day 2018: The Future of Core, Intel GPUs, 10nm, and Hybrid x86

by Dr. Ian Cutress on December 12, 2018 9:00 AM EST- Posted in

- CPUs

- Memory

- Intel

- GPUs

- DRAM

- Architecture

- Microarchitecture

- Xe

Intel’s First Fovoros and First Hybrid x86 CPU: Core plus Atom in 7 W on 10 nm

Perhaps someone will correct me, but I can’t ever remember a time when Intel has put multiple x86 cores of different configurations on the same bit of silicon (ed: Intel Edison). Ever since Arm starting doing it with its big.Little designs in smartphones, a perennial question was if Intel was going to do something similar, either with big and small Atom cores, or by moving a high-performance Core into the mix. When Intel left the smartphone and tablet market, we assumed the idea was dead. But, like a reanimated zombie, it has risen from the grave. Enter Intel’s Hybrid x86 CPU.

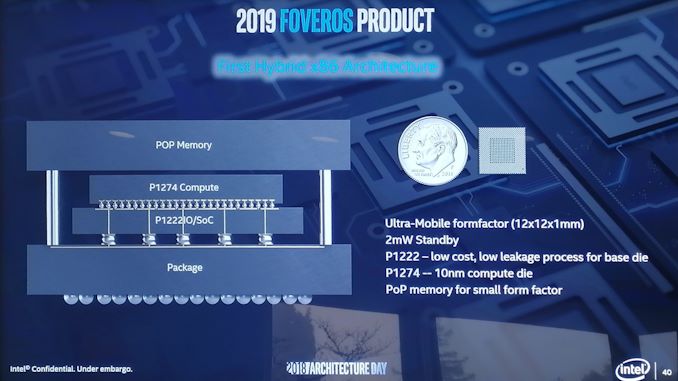

This tiny 12x12 package is built using Intel’s Fovoros technology, using a 22FFL IO chip as the active interposer connected with TSVs to a 10nm die that contains both a single Sunny Cove core and four Atom (Tremont?) cores. This tiny chip is smaller than a dime, and is designed to have a 2 mW standby power. It would appear that this chip is destined for mobile devices.

Here’s the manufacturing diagram, showing the idea that POP memory is placed over the Fovoros design to give the final product. Very much like a mobile chip.

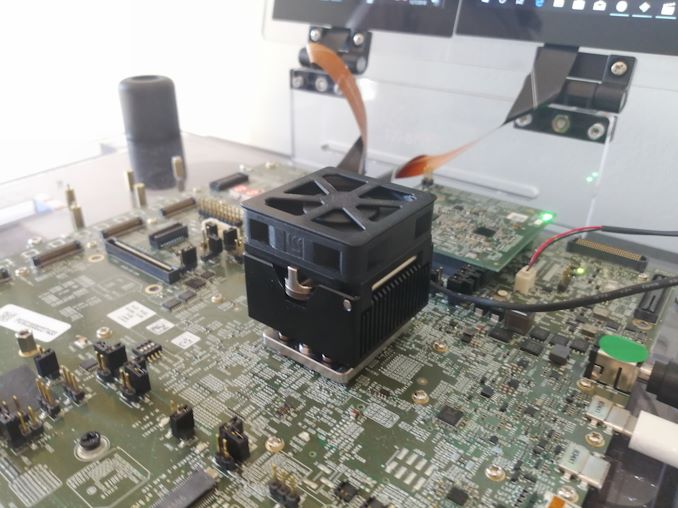

The demo system that Intel had on display looked similar to the previous Sunny Cove design, however this heatsink was smaller and it had a few different connectors. We were told that this chip will support PCIe for M.2 as well as UFS, both of which are found in mobile. There also looked like a couple of SIM card connectors on this motherboard.

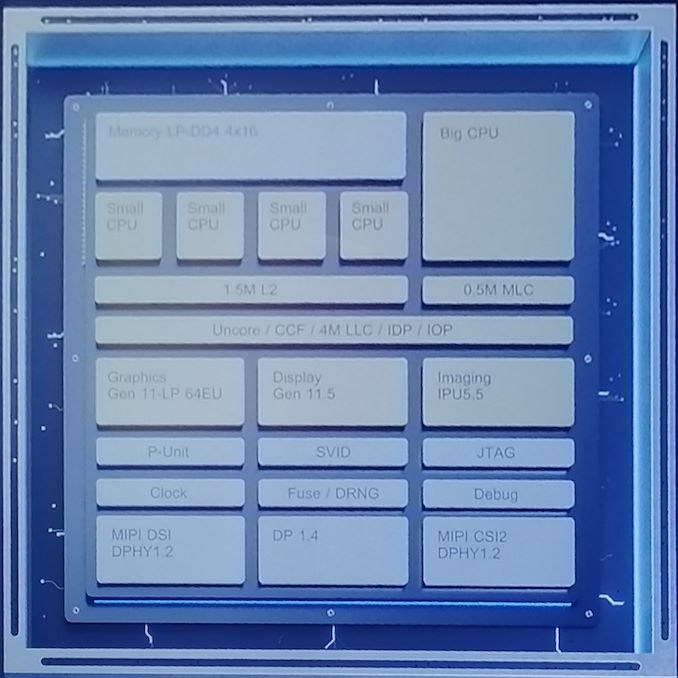

The key part of this discussion however is this block diagram that was on one of the Intel slides. Here we see a single ‘Big CPU’ with 0.5 MB of private medium level cache, four ‘Small CPU’s with a shared 1.5 MB L2 cache, an uncore that has 4MB of last level cache, a quad-channel memory controller (4x16-bit) with support for LPDDR4, a 64 EU design with Gen11 graphics, the Gen 11.5 display controller, a new IPU, MIPI support with DisplayPort 1.4, and all of this in a tiny package.

Seriously though, this has the potential to be a large revenue stream for Intel. They’ve made this chip, which allows the cores to enter C6 sleep states when not in use, that has a die size smaller than 12x12mm (144 mm2), and target the sub-7W fanless device market. That’s with a big Core, four Atom cores, and a GT2 64 EU design.

Intel actually says that the reason why this product came about is because a customer asked for a product of about this performance but with a 2 mW standby power state. In order to do this, Intel created and enhanced a number of technologies inside the company. The final product is apparently ideal for the customer, however the chip will also be made available for other OEMs.

In our Q&A session with the senior members of Intel, it was clear that this technology is still in its infancy, and Intel now has a new toy to play with. Jim Keller stated that internally they are trying lots of new things with this technology to see what works and what would make a good product, so we should be seeing more Foveros designs through 2019 and 2020.

148 Comments

View All Comments

nathanddrews - Wednesday, December 12, 2018 - link

I know the meme about gaming on Intel graphics, but if they implement Adaptive Sync *combined* with some sort of low framerate compensation, it would make gaming on Intel IGP much less hilarious. Can Intel license FreeSync without using AMD GPU inside? I know FreeSync worked on KLG, but that had an AMD GPU.RarG123 - Wednesday, December 12, 2018 - link

Like many of AMD's things, FS's an open standard and royalty free. Anyone can use it.Ryan Smith - Wednesday, December 12, 2018 - link

More specifically, Freesync 1 just AMD's implementation of DisplayPort Adaptive Sync. Intel has to build their own implementation in their display controller and driver stack, but past that all the signaling aspects to the monitor are standardized.Topweasel - Wednesday, December 12, 2018 - link

Ryan, I thought that was reversed, that AMD worked on adding Adaptive Sync into the specs and worked on making sure it's implementation matched what they were doing with Freesync.kpb321 - Wednesday, December 12, 2018 - link

IIRC it's a bit of both. Adaptive Sync was present in the eDP standard for things like laptop monitors or tablets as a power saving feature. AMD brought this to the desktop side of things to use for variable framerates in games and helped the standard bring it over too.edzieba - Wednesday, December 12, 2018 - link

'Adaptive Sync' is effectively the eDP Panel Self Refresh ported over to the full DP spec.drunkenmaster - Wednesday, December 12, 2018 - link

Freesync utilises adaptive sync. Adaptive Sync is the technology on the screen side, a screen must support adaptive sync to be used by Freesync. Freesync is just the AMD side of it. If a adaptive sync capable screen is detected you can turn on freesync in drivers. Adaptive sync was a standard written up and proposed by AMD and given to I forget who it is now, Displayport group direct or to Vesa. They accepted it and implemented it pretty quickly but as with all things standards take a long time for get integrated into the next cycle or two of products.Anyone can use Adaptive sync panels, no one but AMD can use freesync as it's something specific to their hardware and drivers. intel will produce their own specific driver/implementation and just connected to adaptive sync panels in the same way.

porcupineLTD - Wednesday, December 12, 2018 - link

So Intel is going straight to chiplets on interposer, it will be interesting to see if AMD adopts this with Zen 3 or waits until Zen 4. Anyway its nice to see competition doing its job.Alexvrb - Wednesday, December 12, 2018 - link

We don't know yet exactly how much logic Intel is moving to the interposer. It looks awesome for mobile form factors! I think they will face some challenges to bring it to high-TDP desktop solutions, though.ajc9988 - Wednesday, December 12, 2018 - link

http://www.eecg.toronto.edu/~enright/micro14-inter... http://www.eecg.toronto.edu/~enright/Kannan_MICRO4... https://youtu.be/G3kGSbWFig4 https://seal.ece.ucsb.edu/sites/seal.ece.ucsb.edu/... https://www.youtube.com/watch?v=d3RVwLa3EmM&t=...