Intel at Hot Chips 2018: Showing the Ankle of Cascade Lake

by Ian Cutress on August 19, 2018 7:30 PM EST- Posted in

- CPUs

- Intel

- Spectre

- AVX-512

- Meltdown

- Cascade Lake

- Optane DIMMs

- VNNI

Making the Most of Memory: Optane DC Persistent Memory

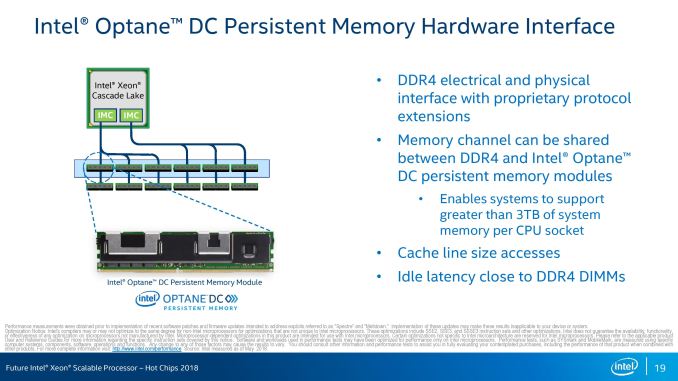

The week before Computex, Intel announced its new Optane DIMMs, and stated that they will be coming to market in three capacities: 128GB, 256GB, and 512GB. The new persistent memory was explained as being a high capacity SSD with that acts as DRAM with similar latencies, available to hold large databases or enable systems to quickly recover from power loss to improve uptimes.

The Hot Chips presentation confirms that the new Optane DIMMs will be enabled at one per memory channel, allowing a single socket to contain six memory modules and six Optane DIMMs at once. For those counting along at home, that is a 128 GB LRDIMM + 512 GB of Optane per channel, or 3840GB per socket.

What this doesn’t state is if Optane will be supported on all processors, or select high-memory SKUs at extra cost. We have seen a few prices flying around for the 512 GB DIMMs, although we cannot verify this. Intel’s own @IntelBusiness Twitter account recently posted this picture, attempting to show that the DIMMs were shipping.

I’m pretty sure the people on the left are making the money hand gesture

If Intel is shipping Optane DIMMs in this quantity already, that means that high-profile customers that are part of Intel’s Early Sampling program are already buying them in bulk quantities. It will be interesting to see if they ever post any data about the product.

Unanswered Questions

Sure, it is frustrating that Intel has not opened the lid fully on Cascade Lake yet. The pure takeaway I can give you is that I suspect the processors will be optimized for efficiency and frequencies will improve, but the core designs will likely look very much the same as we have now. Intel will be using the opportunity, alongside the DIMMs and VNNI, to offer a product that has a number of the Spectre and Meltdown variants fixed in hardware. A lot of people are waiting for these parts, and are prepared to pay for them. It will be interesting to see what the pricing will be later in the year.

31 Comments

View All Comments

Yojimbo - Sunday, August 19, 2018 - link

It's also very big in China.abufrejoval - Monday, August 20, 2018 - link

What about the Control Flow Integrity extensions announced in 2016? Are they mentioned anywhere? Does anyone know what AMD is doing about them?https://software.intel.com/sites/default/files/man...

HStewart - Monday, August 20, 2018 - link

"Does anyone know what AMD is doing about them?"That is real good question and thanks for the Link? - I would be curious about what CPU's will have these extensions. My guess initially it will be part of hardware / software changes mention here. From a quick look at document , it looks primary aim at OS developers especially with mention of task switch.

As for your original question, My guess is that AMD will be adding similar instruction in a future - it just makes it hard for OS developers - unless AMD Licenses the additions so it has similar instructions.

iAPX - Monday, August 20, 2018 - link

Why and how "Mitigation" becomes "Fix"?!?Intel is clear about their lack of Fix again, but only mitigations. In the article it's not the same story.

moozooh - Monday, August 20, 2018 - link

The main reason is likely that CPU R&D cycle normally takes some 2+ years, and the Spectre/Meltdown vulnerabilities were only fully understood sometime midways during Cascade Lake's hardware design cycle where only minor architectural changes could be made. I believe you can only expect full-scale fix in microarchitectures that entered its initial development phases in late 2017 or so. Which means they won't enter the market until mid-2019 at the earliest. So, come back for Ice Lake and its sister families I guess.HStewart - Monday, August 20, 2018 - link

I believe the difference is "Mitigation" is actually done in software or microcode downloaded to chip - but "Fix" is actually a change in actual hardwareedzieba - Monday, August 20, 2018 - link

There is no "fix" without removing Speculative Execution just like there is no hardware "fix" for buffer over/underruns. The fix is in software design, the mitigation is in hardware to compensate for the change in software design.HStewart - Monday, August 20, 2018 - link

I believe that with Spectra 1 - this appears not to required CPU change and others similar to this - Spectra 2 requires no instructions and Spectra 3 requires no hardware changesNot sure about other changes but keep in mind kernal can prevent rogue programs for cause problems but will slow system down by using io protection technique - only thing is what kind of perormance hurt is does this cause - this can fix in hardware with new hardware that the OS

To me as OS developer in the late 80's and early 90's, my knowledge now maybe limited - but cause of change in job - but it pretty sick that OS developers and CPU have spend resource to correct issues for situation with hackers and such to exploit hardware. Keep in mind these problems don't just effect Intel but also include ARM and AMD cpus.

HStewart - Monday, August 20, 2018 - link

A link for the top part - of course part of this is just my opinion based on my previous experience as OS developerhttps://en.wikipedia.org/wiki/Meltdown_(security_v...

I did notice a real CPU defect in IBM 486SLC - when switching from 286 protected mode 386 protected mode te IBM 486SLC had a defect according to IBM that the cache was inverted causing exception and hard lock as occur. I believe this was track down in early 90's

Elstar - Monday, August 20, 2018 - link

"Variant 1 is still to be tackled at the OS level". I wish Intel were more clear about this. They clearly views variant 1 as a problem for any and all software to solve, not just OS/VMM software. The only thing magical about the OS/VMM is that they're more popular attack vectors.