The Samsung Galaxy S9 and S9+ Review: Exynos and Snapdragon at 960fps

by Andrei Frumusanu on March 26, 2018 10:00 AM ESTThe Exynos 9810 - Introducing Meerkat

The Exynos 9810 made a lot of noise this year as S.LSI made astounding claims of up to 2x better single-threaded performance and a 40% uplift in multi-threaded performance. We exclusively covered the first public disclosure of the microarchitecture later in January and showed that Samsung’s performance claims were not farfetched at all. Before we got back to the CPU core, let’s see what else the Exynos 9810 brings to the table.

| Samsung Exynos SoCs Specifications | |||

| SoC | Exynos 9810 | Exynos 8895 | |

| CPU | 4x Exynos M3 1c@2.7, 2c@2.3, 3-4c@1.79 GHz 4x 512KB L2 4096KB L3 4x Cortex-A55 @ 1.79 GHz No L2 512KB L3 |

4x Exynos M2 @ 2.314 GHz 2048KB L2 4x Cortex-A53 @ 1.690GHz 512KB L2 |

|

| GPU | Mali G72MP18 | Mali G71MP20 @ 546MHz |

|

| Memory Controller |

4x 16-bit CH LPDDR4x @ 1794MHz |

4x 16-bit CH LPDDR4x @ 1794MHz 28.7GB/s B/W |

|

| Media | 10bit 4K120 encode & decode H.265/HEVC, H.264, VP9 |

4K120 encode & decode H.265/HEVC, H.264, VP9 |

|

| Modem | Shannon Integrated LTE (Category 18/13) DL = 1200 Mbps 6x20MHz CA, 256-QAM UL = 200 Mbps 2x20MHz CA, 256-QAM |

Shannon 355 Integrated LTE (Category 16/13) DL = 1050 Mbps 5x20MHz CA, 256-QAM UL = 150 Mbps 2x20MHz CA, 64-QAM |

|

| ISP | Rear: 24MP Front: 24MP Dual: 16MP+16MP |

Rear: 28MP Front: 28MP |

|

| Mfc. Process |

Samsung 10nm LPP |

Samsung 10nm LPE |

|

At the heart of the Exynos 9810 we see four Exynos M3 CPU cores, which run at thread-count dependent maximum frequency. This ranges from up to 2.7GHz in single-threaded scenarios, to 2.3GHz in dual-core mode, and 1.79GHz in full quad-core mode.

Alongside the big performance CPUs we also see Samsung’s introduction of Cortex-A55 cores in a quad-core configuration running at up to 1.79GHz (down from the MWC units, which were running at up to 1.9GHz). The interesting thing to note is that unlike the Snapdragon 845, the A55 cores in the Exynos are in their own cluster and not shared with the M3’s.

The GPU is a new Mali G72MP18 running at up to 572MHz. The GPU configuration was a surprise here as not only did Samsung opt to go for a smaller configuration than last year’s MP20, but the clock frequency also hasn’t increased much from the Exynos 8895’s 546MHz.

On paper, the Exynos 9810 has a stronger modem than the Snapdragon 845 as it supports up to 6x carrier aggregation vs the S845’s 5xCA. The upload streams also support 256-QAM which allows for 33% higher upload speeds compared to the Exynos 8895 and Snapdragon’s modems.

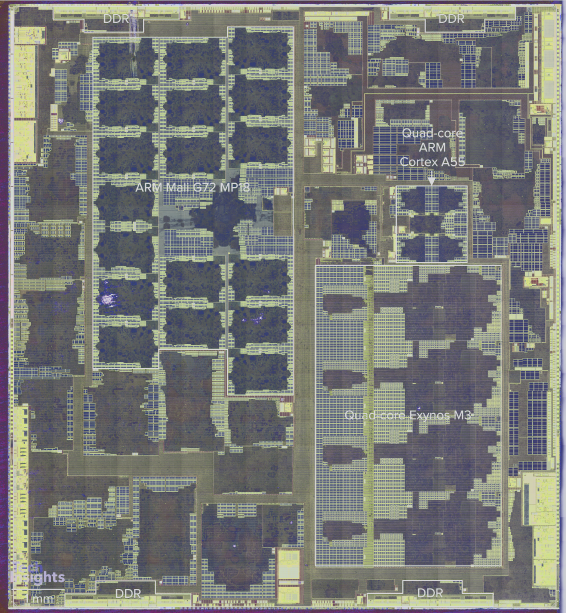

Exynos 9810 Floor Plan. Image Credit TechInsights

TechInsights really delighted us this time around as they also released a die shot of the Exynos 9810 last week. The 9810 comes in at 118.94mm², which is 14% bigger than the 8895’s 103.64mm². Qualcomm seems to have an edge in total die size and we don’t have to look very closely to notice why.

At 20.23mm² the Exynos M3 complex is absolutely massive compared to other mobile SoC CPUs. At 3.46mm² for the core and accompanying L2 the Meerkat core is over twice as big as the 1.57mm² of the A75+L2 in the Snapdragon 845, granted that the latter has half the L2 cache. Meerkat indeed almost matches Apple’s Monsoon cores in the A11 which come in at 2.68mm² - but only if one takes into account the L2 cache of the M3 for which I roughly estimate 0.88mm². Apple also has a slight density advantage due to TSMC’s 10FF manufacturing node.

Nevertheless, at a total of 22.1mm² for both clusters Samsung has thrown down a lot of silicon for the CPU complexes, far more than Apple’s 14.48mm² and Qualcomm’s 11.39mm².

An interesting aspect we can see in the die shot is the way that Samsung arranges the L3. Indeed we reached out again to ARM for clarification on if the DSU allows third-party cores to be used, and contrary to we had been told last year, ARM doesn’t enable third-party cores to be connected. This means that the L3 we see here on the M3’s are of Samsung’s own design. At 4MB, the cache is quite big, but as mentioned, the layout is unlike anything we’ve seen before as it looks like not only does Samsung distribute the L3 SRAM banks in a row/column, but the L3 arbitration logic and L3 tags are also distributed among the banks alongside each M3 core.

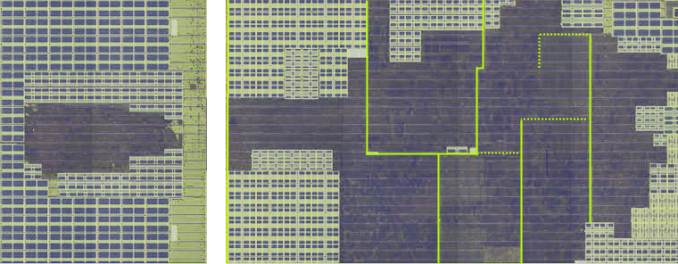

Image Credit TechInsights

Image Credit TechInsights

Looking closer at the core we see two L2 banks (512KB total) along with their tag buffers on the left side. At the top middle we see what is likely the 64KB L1D cache with the load/store engine. On the right side, likely on the bottom, we see the L1I cache as well as other front-end related memories. Unfortunately Samsung’s physical implementation here is a sea of gates and it’s hard to make out the individual CPU engines.

The Cortex-A55 cluster looks quite similar to the Exynos 8895’s A53 cluster – this is due to the lack of per-core L2’s and only a shared 512KB L3 that essentially acts as a shared L2. The performance degradation of the A55s not having L2’s is offset somewhat by the fact that the L3 is run at the same frequencies as the cores – eliminating the need for asynchronous bridges between the cores and the cache and thus reducing the L3 cache latency compared to a normal DSU configuration.

Finally the last interesting take-away from the die shot is the GPU. The Mali G72MP18 comes in at a total of 24.53mm² which is smaller than last year’s >~32mm² behemoth based on the Mali G71MP20. Here it’s clear just much of an advantage Qualcomm has as the Adreno 630 with its 10.69mm² is outright tiny compared to the Mali and even has a significant lead even over Apple’s A11 GPU which comes at 15.28mm².

2.9GHz.. 2.7GHz .. 2.3GHz ... 1.79GHz?? Which is it?

One of the bigger discussion points about the Exynos 9810 was its clock frequency. Samsung had initially announced a peak clock frequency of 2.9GHz but immediately that seemed unlikely given S.LSI’s history of backing down on their initial frequency claims.

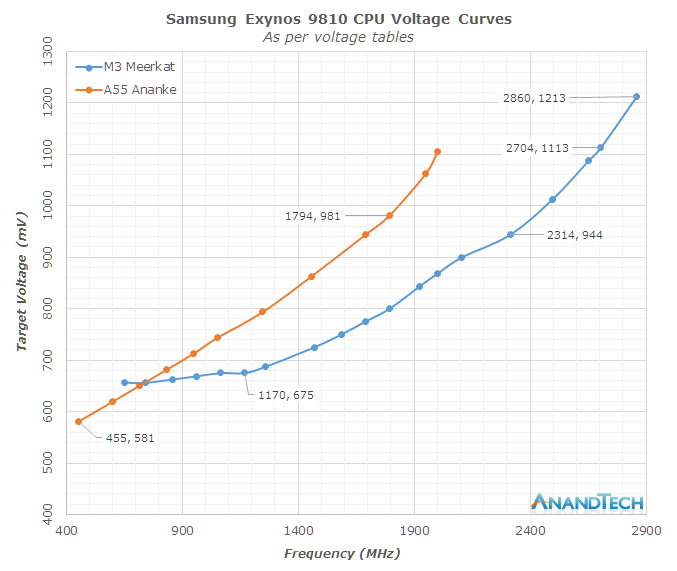

Looking at the voltage tables of the Exynos 9810 points out quite a wide range of voltages for the M3 cores, but it’s the far end that seems quite problematic. To actually reach the initially advertised state of 2.9GHz (2860MHz), it takes an extremely high voltage of 1213mV. Backing down to 2704MHz with which the Galaxy S9 is released ends up with an already drastic decrease of 100mV. Historically Samsung has always had quite high voltages at the far end of the frequency tables as it seems they optimise the physical implementation for leakage and power, which in turn requires higher voltages to reach high frequencies.

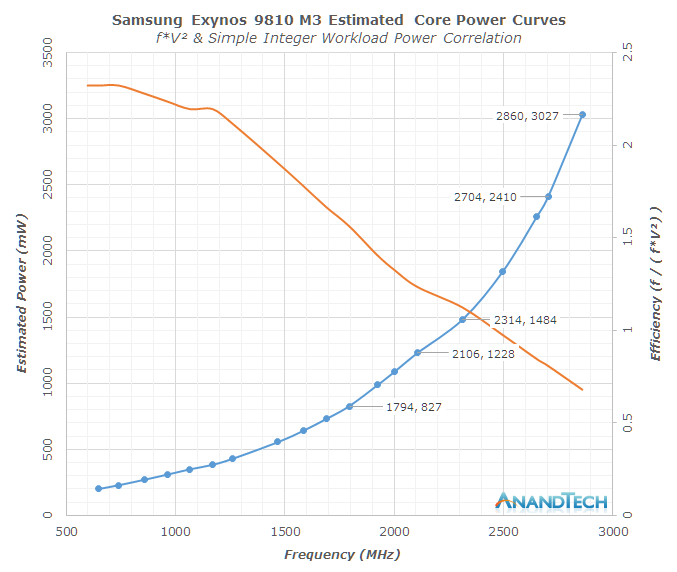

When looking at the power curves correlated with our traditional integer power virus we see that there’s an immense increase in power consumption at the higher frequencies. Indeed going from 2.3GHz to 2.9GHz would have doubled power usage, and even 2.7GHz comes at a steep power price. Given that power usage scales roughly along the lines of voltage cubed, the SoC's efficiency suffers with the increased frequency. The good news here is that Samsung’s efficiency curve is quite steep and linear, that means backing down on frequency should see significant efficiency gains.

Samsung’s decision to limit 2+ core frequencies makes sense in the context of thermal constraints. Even if a CPU core is very efficient at its peak performance, it’s just physically not possible to run multiple cores at peak performance as the SoC just lacks the required thermal dissipation. It’s also important to emphasise this difference between power usage and efficiency: This is no Snapdragon 810 situation where we have high power but with lacking performance. Total energy usage of the M3 should thus be equal to a lower performance core which uses less power.

The only comment I’d like to add here is that I think Samsung would have done a lot better if the M3 cores had been split into a 2+2 configuration with separate frequency and voltage planes. This is something we'll get back to in the battery life section of the review.

I’ve had a look through Samsung’s scheduler and DVFS mechanisms which controls the switching between the 1/2/3/4 core modes and generally I’ve been unimpressed by the implementation. Samsung had made use of hot-plugging to force thread migrations between the cores which is an inefficient way of implementing the required mechanism. The scheduler is also tuned extremely conservatively when it comes to scaling up performance, also something we’ll see the effects of in the system performance benchmarks.

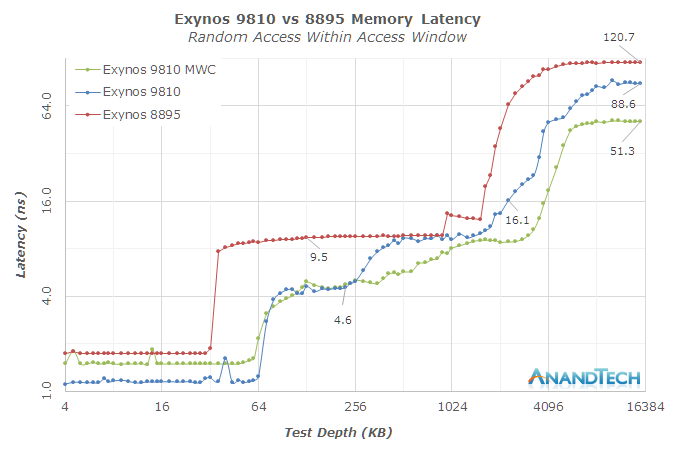

Lastly, I noticed that the commercial unit we acquired had quite different DVFS settings that I was unable to reproduce the excellent memory latency scores I had measured on the launch event devices at MWC. This means that the memory performance is going to be less than I had anticipated, and metrics such as full random access latency actually saw a degradation compared to the Exynos 8895.

190 Comments

View All Comments

goatfajitas - Thursday, March 29, 2018 - link

That is simply incorrect. Not even remotely close to being correct.Dr. Swag - Monday, March 26, 2018 - link

The graphs on the spec page are kinda confusing me. Are the bars on the right side the performance? Oh the left side, are the numbers indicating average power and the bars the total power? You might want to make that a bit more clear, since it took me a while to figure out.tuxRoller - Monday, March 26, 2018 - link

He states that the left axis has two numbers (average power & total energy used), and given the title is the graph (spec) the right axis must be the score achieved. If you look at the bottom of the graphs it has two arrows that point in opposite directions that say something like lower is better (for left axis) and higher is better (for right axis).jospoortvliet - Tuesday, March 27, 2018 - link

See bottom of the graph. Left is power used, right is performance achieved for that older. There is a trade off, as seen in the later run with power saving on: performance for Samsung drops to 2016/2017 level but power usage for the task (and thus efficiency) is ahead of everyone. Andrei attempted to calculate between this and full power what the efficiency would be when the Samsung SOC was tuned to perform like the Qualcomm and estimated a gap of 4-8%. Not too bad but all of it overshadowed by the horrible DFS setting which kills day to day performance.tuxRoller - Tuesday, March 27, 2018 - link

He actually says that if you extrapolate the efficiency in PS to match the perf is the sd845 you'd still see the efficiency (of the 9810) lagging.I'd be interested in seeing the efficiency of the sd845 if you reduced it's perf to those of the 9810 when running in PS.

lilmoe - Wednesday, March 28, 2018 - link

Efficiency @max load =/= @average workload. This isn't a workstation chip.tuxRoller - Wednesday, March 28, 2018 - link

Obviously, that's the whole point.What I'm speaking of is extrapolated efficiency in BOTH directions. We've seen the exynos perf/Joule with both the default governor and the power saving governor. What we haven't seen is the something similar for the 845. It too is going to have it's highest efficiency somewhere towards the middle of its OPPs.

Iow, it would be nice to have the perf/Joule curve over the various OPPs for both of these chips.

halcyon - Monday, March 26, 2018 - link

Lorem ipsum dolor sit amet, consectetur adipiscing elit, sedthat's in the "Video evaluation" section

Great review! the kind I expect from Anandtech.

Andrei Frumusanu - Monday, March 26, 2018 - link

Had forgotten to replace those paragraphs, fixed.Ian Cutress - Monday, March 26, 2018 - link

Fixed :)