The AMD Radeon RX Vega 64 & RX Vega 56 Review: Vega Burning Bright

by Ryan Smith & Nate Oh on August 14, 2017 9:00 AM ESTThe Vega Architecture: AMD’s Brightest Day

From an architectural standpoint, AMD’s engineers consider the Vega architecture to be their most sweeping architectural change in five years. And looking over everything that has been added to the architecture, it’s easy to see why. In terms of core graphics/compute features, Vega introduces more than any other iteration of GCN before it.

Speaking of GCN, before getting too deep here, it’s interesting to note that at least publicly, AMD is shying away from the Graphics Core Next name. GCN doesn’t appear anywhere in AMD’s whitepaper, while in programmers’ documents such as the shader ISA, the name is still present. But at least for the purposes of public discussion, rather than using the term GCN 5, AMD is consistently calling it the Vega architecture. Though make no mistake, this is still very much GCN, so AMD’s basic GPU execution model remains.

So what does Vega bring to the table? Back in January we got what has turned out to be a fairly extensive high-level overview of Vega’s main architectural improvements. In a nutshell, Vega is:

- Higher clocks

- Double rate FP16 math (Rapid Packed Math)

- HBM2

- New memory page management for the high-bandwidth cache controller

- Tiled rasterization (Draw Stream Binning Rasterizer)

- Increased ROP efficiency via L2 cache

- Improved geometry engine

- Primitive shading for even faster triangle culling

- Direct3D feature level 12_1 graphics features

- Improved display controllers

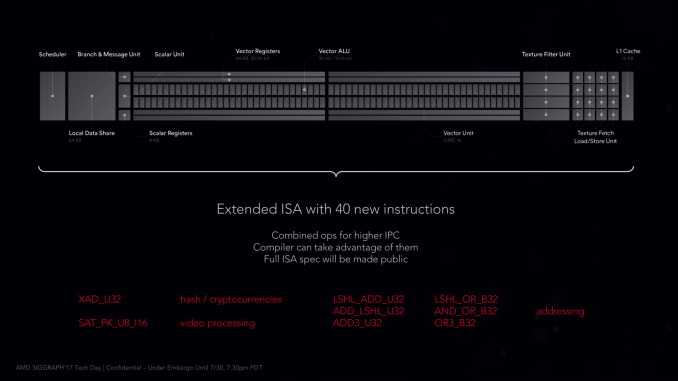

The interesting thing is that even with this significant number of changes, the Vega ISA is not a complete departure from the GCN4 ISA. AMD has added a number of new instructions – mostly for FP16 operations – along with some additional instructions that they expect to improve performance for video processing and some 8-bit integer operations, but nothing that radically upends Vega from earlier ISAs. So in terms of compute, Vega is still very comparable to Polaris and Fiji in terms of how data moves through the GPU.

Consequently, the burning question I think many will ask is if the effective compute IPC is significantly higher than Fiji, and the answer is no. AMD has actually taken significant pains to keep the throughput latency of a CU at 4 cycles (4 stages deep), however strictly speaking, existing code isn’t going to run any faster on Vega than earlier architectures. In order to wring the most out of Vega’s new CUs, you need to take advantage of the new compute features. Note that this doesn’t mean that compilers can’t take advantage of them on their own, but especially with the datatype matters, it’s important that code be designed for lower precision datatypes to begin with.

213 Comments

View All Comments

Otritus - Monday, August 14, 2017 - link

in the first page on the AMD Radeon RX Series Specification Comparison chart it says vega 56 has 3585 shaders instead of 3584 shadersOtritus - Monday, August 14, 2017 - link

gtx 1070 msrp is 349, price drop after 1080 tiTargon - Monday, August 14, 2017 - link

I'd be surprised if we don't need another two to three months to see how the Vega performance ends up with the expected driver updates. Every high end card from AMD and NVIDIA gets at least one big driver update to add 5-10 percent performance in games.Cellar Door - Monday, August 14, 2017 - link

Thanks for your excellent work Ryan.redwarrior - Tuesday, August 15, 2017 - link

Did you noter that the duynamic cache controller that AMD has touted is disabled at this point since the drivers have not been perfected to operate the cache efficiently. Once they solve that issue performance will jump anywhere from 10 to 15%. There is also some feature with the shaders that is also still disabled. All in all if we exercise a little patience Vega 64 should be a credible performer about half way between 1080 and 1080 Ti in performance. I hope when the drivers are more mature that people will do further reviews on these Vega offerings.AndrewJacksonZA - Tuesday, August 15, 2017 - link

Thank you Ryan.ddriver - Monday, August 14, 2017 - link

It seems amd still have a long way to do with the drivers, despite vega being so late... Judging by the battlefield result, a title that has both optimized for amd rather than exclusively for nvidia, and has been optimized on driver level by amd, this is where vega's actual graphics capabilities lie when it comes to the actual hardware, between the 1080 and the Ti.The good (for amd) news and bad (for people like me) is that vega looks like it has exceptional compute performance, which means prices will no doubt go through the roof because of the mining craze. This is not bad for gamers, since nvidia seems like the better value, but people who need compute for stuff other than mining will have to wait a while before vega could be bought at a good price.

TheinsanegamerN - Monday, August 14, 2017 - link

If we have to rely on AMD optimizing every single game for VEGA, we will never see its true potential. AMD couldnt manage to do it right in a year and some change.ddriver - Tuesday, August 15, 2017 - link

nvidia is pretty much doing that, they spend a tremendous amount of money doing other's work, money that amd is not in the position to spendScabies - Monday, August 14, 2017 - link

SR-IOV?