Sizing Up Servers: Intel's Skylake-SP Xeon versus AMD's EPYC 7000 - The Server CPU Battle of the Decade?

by Johan De Gelas & Ian Cutress on July 11, 2017 12:15 PM EST- Posted in

- CPUs

- AMD

- Intel

- Xeon

- Enterprise

- Skylake

- Zen

- Naples

- Skylake-SP

- EPYC

Memory Subsystem: Latency

The performance of modern CPUs depends heavily on the cache subsystem. And some applications depend heavily on the DRAM subsystem too. We used LMBench in an effort to try to measure cache and memory latency. The numbers we looked at were "Random load latency stride=16 Bytes".

| Mem Hierarchy |

AMD EPYC 7601 DDR4-2400 |

Intel Skylake-SP DDR4-2666 |

Intel Broadwell Xeon E5-2699v4 DDR4-2400 |

| L1 Cache cycles | 4 | 4 | 4 |

| L2 Cache cycles | 12 | 14-22 | 12-15 |

| L3 Cache 4-8 MB - cycles | 34-47 | 54-56 | 38-51 |

| 16-32 MB - ns | 89-95 ns | 25-27 ns (+/- 55 cycles?) |

27-42 ns (+/- 47 cycles) |

| Memory 384-512 MB - ns | 96-98 ns | 89-91 ns | 95 ns |

Previously, Ian has described the AMD Infinity Fabric that stitches the two CCXes together in one die and interconnects the 4 different "Zeppelin" dies in one MCM. The choice of using two CCXes in a single die is certainly not optimal for Naples. The local "inside the CCX" 8 MB L3-cache is accessed with very little latency. But once the core needs to access another L3-cache chunk – even on the same die – unloaded latency is pretty bad: it's only slightly better than the DRAM access latency. Accessing DRAM is on all modern CPUs a naturally high latency operation: signals have to travel from the memory controller over the memory bus, and the internal memory matrix of DDR4-2666 DRAM is only running at 333 MHz (hence the very high CAS latencies of DDR4). So it is surprising that accessing SRAM over an on-chip fabric requires so many cycles.

What does this mean to the end user? The 64 MB L3 on the spec sheet does not really exist. In fact even the 16 MB L3 on a single Zeppelin die consists of two 8 MB L3-caches. There is no cache that truly functions as single, unified L3-cache on the MCM; instead there are eight separate 8 MB L3-caches.

That will work out fine for applications that have a footprint that fits within a single 8 MB L3 slice, like virtual machines (JVM, Hypervisors based ones) and HPC/Big Data applications that work on separate chunks of data in parallel (for example, the "map" phase of "map/reduce"). However this kind of setup will definitely hurt the performance of applications that need "central" access to one big data pool, such as database applications and big data applications in the "Shuffle phase".

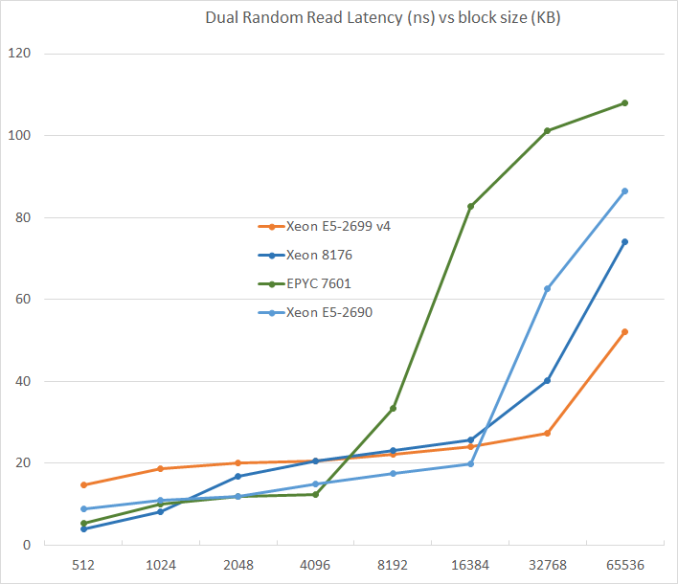

Memory Subsystem: TinyMemBench

To double check our latency measurements and get a deeper understanding of the respective architectures, we also use the open source TinyMemBench benchmark. The source was compiled for x86 with GCC 5.4 and the optimization level was set to "-O3". The measurement is described well by the manual of TinyMemBench:

Average time is measured for random memory accesses in the buffers of different sizes. The larger the buffer, the more significant the relative contributions of TLB, L1/L2 cache misses, and DRAM accesses become. All the numbers represent extra time, which needs to be added to L1 cache latency (4 cycles).

We tested with dual random read, as we wanted to see how the memory system coped with multiple read requests.

L3-cache sizes have increased steadily over the years. The Xeon E5 v1 had up to 20 MB, v3 came with 45 MB, and v4 "Broadwell EP" further increased this to 55 MB. But the fatter the cache, the higher the latency became. L3 latency doubled from Sandy Bridge-EP to Broadwell-EP. So it is no wonder that Skylake went for a larger L2-cache and a smaller but faster L3. The L2-cache offers 4 times lower latency at 512 KB.

AMD's unloaded latency is very competitive under 8 MB, and is a vast improvement over previous AMD server CPUs. Unfortunately, accessing more 8 MB incurs worse latency than a Broadwell core accessing DRAM. Due to the slow L3-cache access, AMD's DRAM access is also the slowest. The importance of unloaded DRAM latency should of course not be exaggerated: in most applications most of the loads are done in the caches. Still, it is bad news for applications with pointer chasing or other latency-sensitive operations.

219 Comments

View All Comments

deltaFx2 - Thursday, July 13, 2017 - link

"Can you mention one innovation from AMD that changed the world?" : None. But the same applies to Intel too, save, I suppose, the founders (Moore and Noyce) contributions to IC design back when they were at Fairchild/Shockley. That's not Intel's contribution. Computer Architecture/HPC? That's IBM. They invented the field along with others like CDC. Intel is an innovator in process technology, specifically manufacturing. Or used to be... others are catching up. That 3-yr lead that INtel loves to talk about is all but gone. So with that out of the way...AMD's contributions to x86 technology: x86-64, hypertransport, integrated memory controller, multicore, just to name a few. Intel copied all of them after being absolutely hammered by Opteron. Nehalem system architecture was a copy-paste of Opteron. It is to AMD's discredit that they ceded so much ground on the CPU microarchitecture since then with badly executed Bulldozer, but it was AMD that brought high-performance features to x86 server. Intel would've just loved to keep x86 on client and Itanium on server (remember that innovative atrocity?). Then there's a bunch on the GPU side (which INtel can't get right for love or money), but that came from an acquisition, so I won't count those.

"AMD exists because they are always inferior". Remember K8? It absolutely hammered intel until 2007. Remember Intel's shenanigans bribing the likes of Dell to not carry K8? Getting fined in the EU for antitrust behaviors and settling with AMD in 2010? Not much of a memory card on you, is there?

AMD gaining even 5-10% means two things for intel: Lower margins on all but the top end (Platinum) and a loss in market share. That's plain bad for the stock.

"Intel is a data center giant have head start have the resources...". Yes, they are giants in datacenter compute. 99% market share. Only way to go from there is down. Also, those acquisitions you're talking about? Only altera applies to the datacenter. Also, remember McAfee for an eye-watering $7.8 bn? How's that working out for them?

Shankar1962 - Wednesday, July 12, 2017 - link

Nvidia who have been ahead than Intel in AI should be the more competent threatHow much market share Intel loses depends on how they compete against Nvidia

Amd will probably gain 5% by selling products for cheap prices

Intel controls 98/99% share so it's inevitable to lose a few % as more players see the money potential but unless Intel loses to Nvidia there is annuphill battle for Qualcomm ARM.

HanSolo71 - Wednesday, July 12, 2017 - link

Could you guys create a Benchmark for Virtual Desktop Solutions? These AMD chips sound awesome for something like my Horizon View environment where I have hundreds of 2 core 4GB machines.Threska - Saturday, July 22, 2017 - link

For VDI wouldn't either an APU setup, or CPU+GPU be better?msroadkill612 - Wednesday, July 12, 2017 - link

Kudos to the authors. I imagine its gratifying to have stirred such healthy & voluminous debate :)milkod2001 - Thursday, July 13, 2017 - link

Are you guys still updating BENCH results? I cannot find there benchmark results for RYZEN CPUs when i want to compare them to others.Ian Cutress - Friday, July 14, 2017 - link

They've been there since the launchAMD (Zen) Ryzen 7 1800X:

http://www.anandtech.com/bench/product/1853

KKolev - Thursday, July 13, 2017 - link

I wonder if AMD'd EPYC CPU's can be overclocked. If so, the AMD EPYC 7351P would be very interesting indeed.uklio - Thursday, July 13, 2017 - link

How could you not do Cinebench results?! we need an answer!JohanAnandtech - Thursday, July 13, 2017 - link

I only do server benchmarks, Ian does workstation. Ian helped with the introduction, he will later conduct the workstation benchmarks.