AMD CPU Updates: 16 Core ThreadRipper w/64 PCIe Lanes This Summer, Epyc Launching June 20th

by Ryan Smith on May 30, 2017 11:57 PM EST- Posted in

- CPUs

- AMD

- Computex 2017

- ThreadRipper

- EPYC

Wrapping up just a bit ago was AMD’s annual Computex press conference. AMD brings their A-game to Computex, and for a good reason: as a PC focused show, it gives them great exposure, but it also allows them to promote their OEM relationships, the latter of which are crucial to AMD’s survival as the CPU underdog. Computex in turn isn’t a venue for deep technical announcements, but it’s a good place to get clarity on AMD’s CPU roadmap.

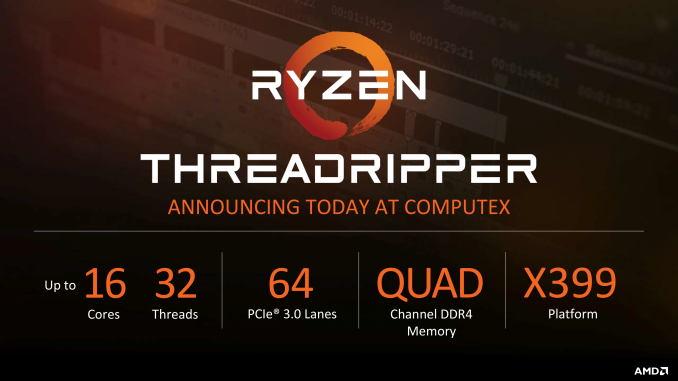

Starting things off then, let’s talk about ThreadRipper. AMD’s previously announced many-core CPU for the high-end PC desktop and workstation market was first announced at Financial Analyst Day a few weeks back. AMD is now in the process of slowly releasing information about the chip to build up interest ahead of its launch – which, before you ask, hasn’t been set yet and is still “this summer”.

At today’s press conference, AMD has confirmed that the 16 core processor will for most purposes be half of an Epyc processor. This means that the two die MCM chip will feature 4 DDR4 channels and a whopping 64 lanes of PCIe, with all 64 lanes being enabled for all ThreadRipper SKUs. This will be broken up into 60+4: 60 lanes directly from the CPU for feeding PCIe and M.2 slots, and then another 4 lanes going to the chipset (with an undisclosed number of lanes then coming off of it) to drive basic I/O, USB, and other features. AMD seems to be particularly relishing the point on PCIe lanes in light of the yesterday’s Intel HEDT announcement, which maxes out at 44 lanes and no chip below $1000 actually has all of them enabled.

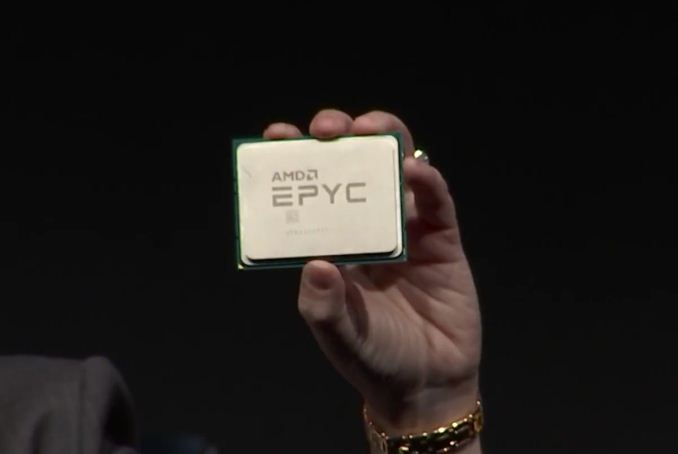

The launch chipset for ThreadRipper will be the X399 chipset (ed: at this point AMD and Intel are literally trying to one-up each other). No details have been released on it thus far, so we’ll have to see what AMD has up their sleeve. But coming so close to the Ryzen launch, it doesn’t sound like it’ll be radically different. Otherwise we’re hoping to grab some pictures of X399 boards at the show today, as those should be on display. The ThreadRipper/Epyc socket in particular should be interesting; the chip is nothing short of massive, and in the one photo AMD has released so far of an Epyc motherboard, the socket looks equally huge.

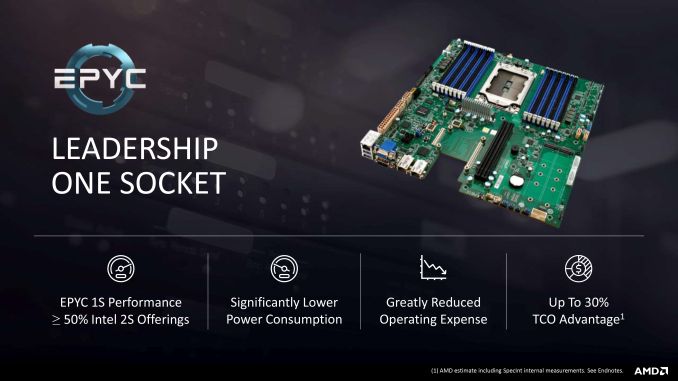

Finally, not to be outdone, AMD’s 32 core & 128 PCIe lane Epyc CPU for servers has also received some news of its own. AMD’s first promising product in the server space in nearly half a decade will be launching on June 20th.

71 Comments

View All Comments

Gothmoth - Wednesday, May 31, 2017 - link

but the intel DIE is denser packed and smaller overall so it has to dissipate more heat over a smaller area too.... it´s not all that simple you know.i doubt it will be higher too, but 16 core skylake-x will be HCC and they are not famous for high clocks either...

vladx - Wednesday, May 31, 2017 - link

Well AMD's move with ThreadRipper forces Intel to show their superiority with higher clocks, hence why Intel didn't yet announce the clocks for HCC parts waiting for AMD's move first.Gothmoth - Wednesday, May 31, 2017 - link

HCC is enterprise... if they could go higher easily they would.. enterprise has the money to pay for it.it´s sound more like thinking from an intel fanboy.

anyway i don´t care i will buy what gives me the most bang for the buck.

vladx - Wednesday, May 31, 2017 - link

Correction, HCC was enterprise-only before, if you've read Intel's Skylake-X recent announcement right here on Anandtech you would've seen that Intel included HCC parts to HEDT as well, that's why I'm saying Intel is waiting on AMD to show their cards first before they reveal their clocks for the 14. 16 and 18 core Skylake-X CPUs.So the fight will be most likely be more PCIe lanes vs higher clocks, whichever suits clients better.

Manch - Wednesday, May 31, 2017 - link

The OP said people worry about the clock speed and ST performance. My reply was to that. If your use case needs clock speed and ST performance, the an HEDT isn't for you. They tend to be clocked lower a good bit. A 4 core speed demon would suit you better. Of course everyone wants more cores, more speed, more cache for less money. That's a another story all together and not the point. ;)vladx - Wednesday, May 31, 2017 - link

64 PCI lanes is awesome but the catch is no doubt significantly slower clocks around 3.2Ghz compared to 3.8-4Ghz of Intel equivalent.PixyMisa - Wednesday, May 31, 2017 - link

If the leaks are correct, the top chips will be 3.5 base, 3.9 boost. Some of the cut-down chips will have slightly higher clocks.3.5/3.9 is great for a 16-core chip.

asdacap - Wednesday, May 31, 2017 - link

I have a feeling that the size is mainly because of the PCI-E lanes. Even a 16 core processor should not be that big. At least they can (relatively) easily upgrade the cpu to 32 or maybe even 64 core cpu.ajp_anton - Wednesday, May 31, 2017 - link

It's big because it's literally two Ryzen dies in one package, which is not as compact as a single 16-core die. The 32-core server CPU is four dies.nevcairiel - Wednesday, May 31, 2017 - link

Indeed, and having 2 dies also has other disadvantages (not to mention that each die is already 2 "modules" internally), I wonder how it fares against Intels real 16-core die.