IDF Fall 2006 - Day 2: Geneseo, Santa Rosa, Memory Roadmap and More

by Anand Lal Shimpi on September 28, 2006 3:43 AM EST- Posted in

- Trade Shows

Santa Rosa Arrives

Intel just recently launched its mobile Core 2 Duo platform, built around the Merom core but using the same 945 Express chipset family that was introduced alongside the Core Duo processors. By keeping the platform the same, Intel ensured a far more seamless transition to the new processors (and kept OEMs somewhat happier) than had it introduced a new chipset and processor at the same time. In Q1 of next year however, Intel will be updating its Centrino platform to catch up to the innovation that was introduced with Core 2 Duo. We've talked about the new platform in the past and it's known by the code name Santa Rosa.

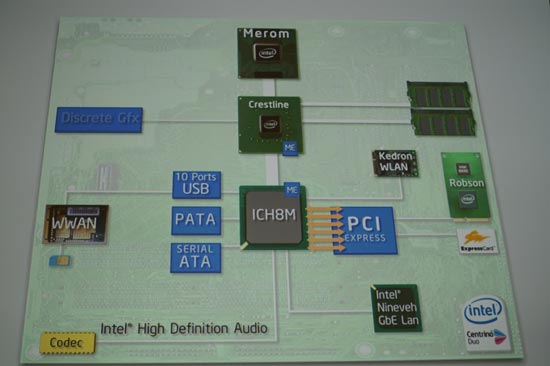

Santa Rosa block diagram

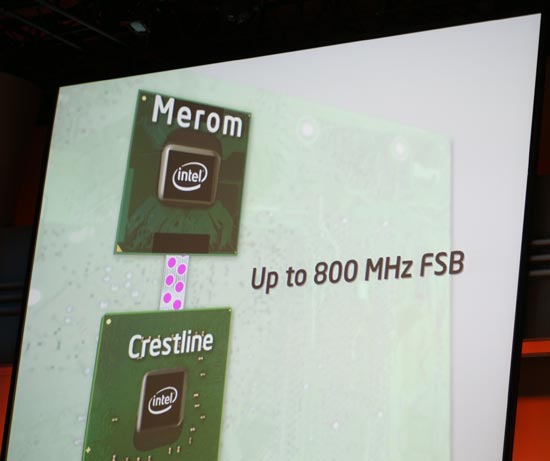

On the processor side, 65nm Merom based Core 2 Duo processors will still be at the heart of Santa Rosa. The difference this time around is that Intel will introduce 800MHz FSB Core 2 Duo processors, compared to the 667MHz Core 2 Duo processors that were just launched.

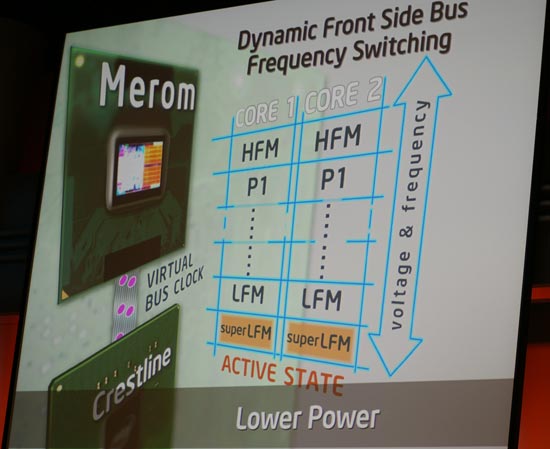

Along with the faster FSB, Intel will for the first time add an adjustable FSB clock frequency to help reduce power. Currently, on battery power, Core 2 Duo based notebooks will operate in a low frequency mode (LFM) at a low voltage. However, this LFM still runs with the FSB clocked at full speed, which is 667MHz in the case of current Core 2 Duo notebooks. With Santa Rosa, Intel is introducing a super low frequency mode (super LFM) that underclocks the FSB from 800MHz to 400MHz, also cutting the CPU speed in half, down to 600MHz from 1.2GHz at its LFM state. With a slower FSB frequency and lower CPU clock speed, Santa Rosa hopes to save more power when idle than its predecessor.

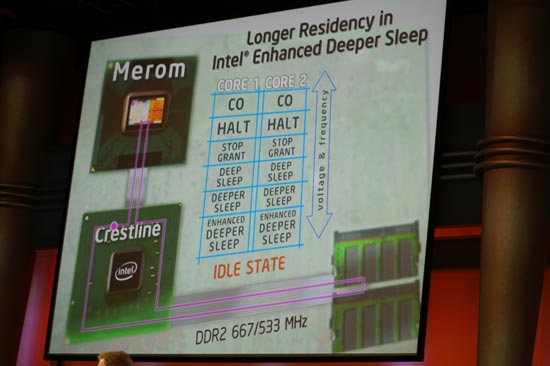

Of course the chipset in Santa Rosa is Intel's mobile 965 solution, codenamed Crestline. In addition to supporting the faster 800MHz FSB, there is one important power saving feature that was added to the chipset. In the Core 2 Duo's lowest power state, often referred to as Enhanced Deeper Sleep, all data in its cache is flushed to main memory and the cache is powered down to conserve battery life. In the current Core 2 Duo platform, if the memory controller is still handling memory requests, it will continually wake the processor up looking for data in its cache, even though the cache is empty.

The new 965 chipset goes through a handshaking process with the CPU so it knows when the Core 2 processor's cache has been flushed, thus knowing not to wake it up until it absolutely needs to. It sounds like a simple fix but it should result in reduced power consumption.

Along with the new chipset comes an updated integrated graphics core, which we have been testing in our labs on the desktop side. Intel insists that the new integrated graphics offers similar average power to the 945G graphics, but under load we're expecting it to consume more as it is a full DX9/PS3.0 part.

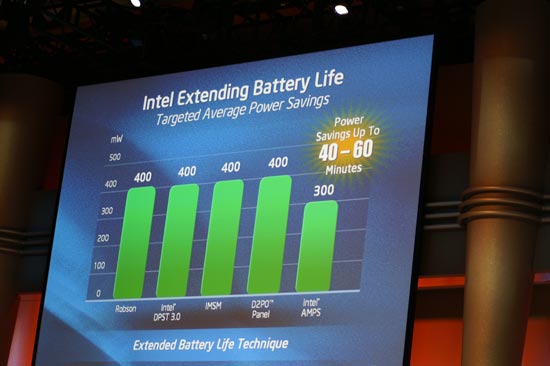

Those are all of the major changes to the chipset, but there are other improvements to the platform that will be joining us with Santa Rosa. Intel's Dadi Perlmutter, Senior VP and General Manager of Intel's Mobility Group gave us an interesting tidbit of information; he stated that for every 1W of average power you can reduce on a notebook, you gain 20 - 30 minutes of battery life. With that in mind, he threw up this slide showcasing all of the areas that Intel is looking to save power in:

We talked about Robson technology yesterday, and it will surely reduce some power consumption by keeping the hard disk spun down as much as possible, but an interesting technology is Toshiba/Matsushita's interlaced display offering. The technology demonstrated is quite simple; when running on battery power, if the display detects that no motion video is being played back, it will function in an interlaced mode (displaying only half the vertical resolution at any given time) to conserve power.

Dadi's demo showed a savings of over 200mW when operating in interlaced mode, and suggesting a savings of close to 400mW for higher resolution and brighter panels than the one being demonstrated.

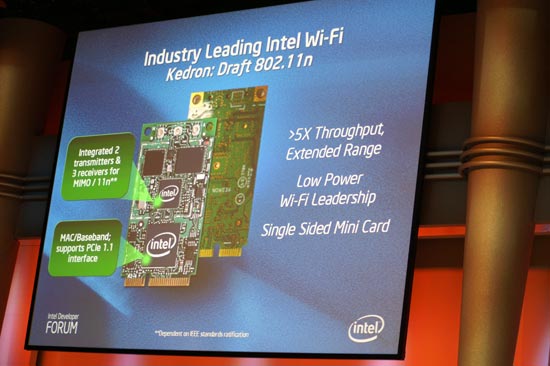

The final discussion of Santa Rosa centered around wireless technologies. A requisite part of Santa Rosa will be Intel's Kedron 802.11n wireless solution, which for the first time in Intel history will be a Centrino bundled wireless solution released before a finalized IEEE spec. The Kedron 802.11n wireless will use the Draft-N spec and Intel assures us that its solution will be significantly better both in performance and interoperability than current Draft-N solutions. We will have to wait and see, but it would be quite surprising for Intel to compromise the quality associated with its Centrino brand by bundling a poor wireless solution; we have high expectations for Kedron and Intel seems confident it can deliver in Q1 of next year.

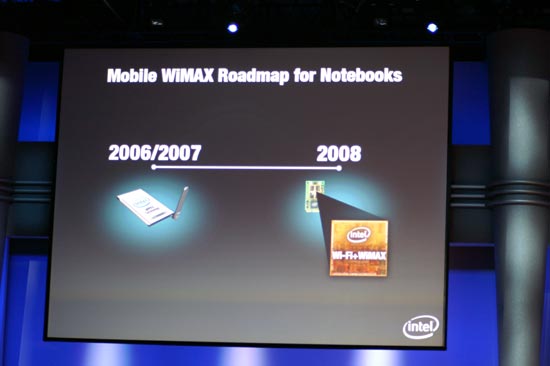

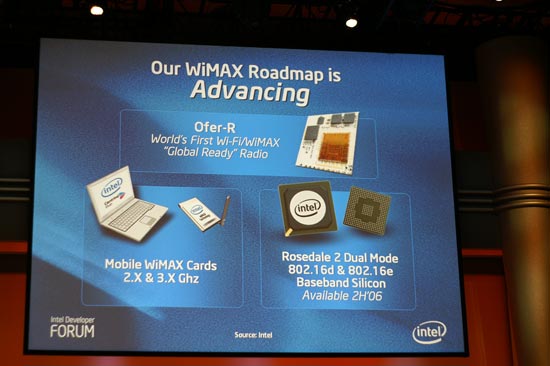

While WiMAX isn't a part of the component list necessary for Centrino certification, Intel will begin offering WiMAX cards for notebooks in 2006/2007; by 2008 you can expect WiMAX integration on the motherboard level.

7 Comments

View All Comments

porkster - Thursday, September 28, 2006 - link

If you ask me, laptop graphics is a major issue at the moment.Intel really needs to bring forth the Santa Rosa chipset to set a new bench level for gfx. x3000 maybe just enough to move upto, but even the power of the gfx intergrations, isn't that great.

Vista will make most laptop's second generation, the day it is released.

johnsonx - Thursday, September 28, 2006 - link

It's been speculated that AMD would have something to show in a hotel room across the street from IDF as they have in past years. So far it seems AMD is silent this year. A bad sign? AMD not as close on quad-core and/or K8-L as everyone has been hoping?What's the industry scuttlebutt on this?

smitty3268 - Thursday, September 28, 2006 - link

I was wondering the same thing. Perhaps K8L won't actually be any faster than current Conroes?fitten - Thursday, September 28, 2006 - link

You know... as much as people say this, it's odd that the aging FSB architecture is in the fastest system on the market right now... even faster than "newer" non-FSB architecture. Sure, it may not post as high synthetic benchmark bandwidth and latency numbers but when running applications, it sure seems to do pretty well. Sure, a new interconnect architecture might make it even faster and cooler but simply because the FSB is "aging" doesn't necessarily imply that it doesn't work.

Xenoterranos - Thursday, September 28, 2006 - link

While I agree with your point, at the crux of the argument is the question about when FSB will be too out dated. We all know it doesn't scale that well, and it's a testament to Intel's engineering teams that they are able to make it work so well. On the Xeons we see them moving toward dual FSB's, considering that we now have dual core processors, maybe this isn't that bad of a sign for the good ol FSB. HyperTransport is making great strides, and I would love to see Intel direct some of it's considerable brainpower at (co?)developing a new system like that instead of finessing all the power they can out of the one they have. I think they really believe that FSB is the way to go right now, but I would seriously doubt they have no plans to move to something like HT in the future.fitten - Friday, September 29, 2006 - link

Intel's serial interconnect that they're working on is called CSI.Clauzii - Thursday, September 28, 2006 - link

I find it kind of funny to see Vista running on MAC OS ;)