Intel Developer Forum Fall 2004: Day 1 Keynote

by Derek Wilson on September 7, 2004 5:11 PM EST- Posted in

- Trade Shows

Pushing Parallelism

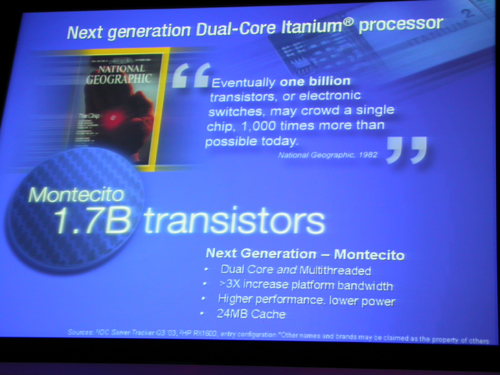

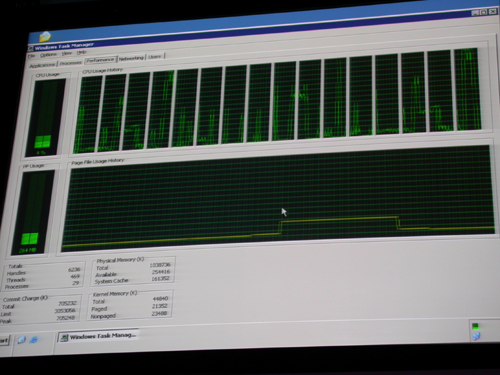

Finally, we have the demo we'd all been waiting for. Intel showed a 4p Itanium server running 4 dual core processors. This results in windows seeing 16 logical processors and reveals a crazy looking task manager window. The reason each dual core processor appears as four is that each core support Hyperthreading. Here's what ctrl+alt+del looks like with 4 parallel 1.7billion transistor dual core Itaniums:

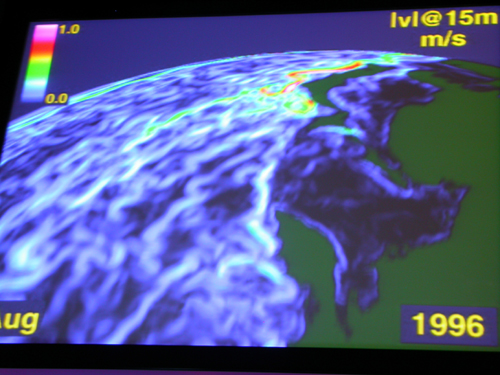

The demo Intel ran on dual core processors was a very complex weather simulator.

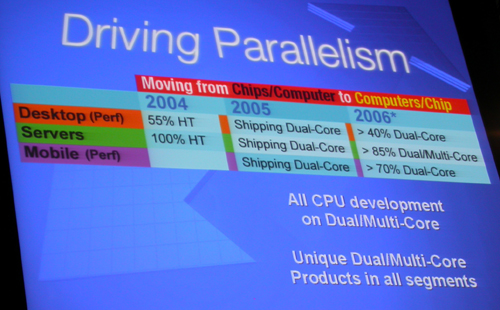

While very cool, such a brief taste of the technology always leaves us wanting more. Unfortunately, Intel is being very tight lipped about their dual core endeavors in other areas. They have stated that dual core processors will be available in 2005, and that they expect some very high adoption rates to push dual core computing to 40% of desktops by 2006, and 85% of servers (which would be dual and multi core). They say the technology is also well suited to mobile devices, but we don't really have any more info than that. It is very clear that Intel will be targeting this area very aggressively as they expect the mobile market to be 70% dual core in 2006.

We were able to get a further lesson in parallelism in Intel's guests from NASA. The Space Administration is apparently working on a supercomputer using and sgi Itanium 2 server targeted at 60 Teraflops of power. This would put it at 50% more compute power than the worlds fastest supercomputer. The supercomputer project is called project Columbia and will feature 10000 processors when completed.

Now that Intel and AMD have both demonstrated dual core processors, it's only a matter of waiting for this technology to come down the pipe, into our labs, and into your homes. Here's to time flying.

We will do some digging while we're here, and hopefully someone will be able to help us discern a few more details about upcoming dual core technology and whatever else Intel may have up their sleeves. It's off to the show floor for now.

28 Comments

View All Comments

IntelUser2000 - Tuesday, September 14, 2004 - link

Ah crap. Posted empty message.Anyways, in response to:

"That's what I like about the Athlon 64, no stupid large caches necessary"

One major thing that people get wrong is that "Imagine Athlon64 or Opteron with 24MB cache". The thing is, AthlonXP and Opteron/Athlon64 didn't get much benefit from cache anyway as Pentium 4 did. We didn't see significant improvements going to Barton with 512KB L2 cache compared to P4, which had much larger performance improvements(Barton Link: http://www.anandtech.com/cpuchipsets/showdoc.aspx?... Pentium 4 Northwood Link: http://www.anandtech.com/cpuchipsets/showdoc.aspx?...

Comment from Barton review at last page:"It is very interesting to note the relatively small performance improvement that resulted from the additional L2 cache, at least when you compare the impact of Barton to the impact Northwood had on the Pentium 4."

If you look at the reviews, there are times where Barton is basically equal to the Thoroughbred B core, even considering that Thoroughbred B has 3.8% higher clock than Barton, doubling of L2 cache from 256KB to 512KB didn't do much as 512KB cache did on P4.

So if AMD puts the current Itanium's 6MB L3, not only there won't be a significant performance increase, the performance scaling would rapidly decrease. That's the reason why S754 Sempron isn't much worse than full-blown Athlon64 with double L2 cache. So even if AMD has the resources or the will to put 6MB L2, it won't benefit Opteron/A64 much.

Look at this link: http://www.anandtech.com/cpuchipsets/showdoc.aspx?...

I mean, how can two processors that are targeted at such different markets, Sempron for value and A64 for mainstream, and cache size, have such little difference in performance? Why get A64 2800+ Newcastle when Sempron does same with 1/2 the price? So I say AMD will be lucky to get 10-15% performance increase by going to 24MB cache at this scaling.

It's not the ability of AMD to put 24MB L2 or L3 cache that's the problem, its the performance that's squeezed out of that.

Itaniums however(especially with Montecito), love bandwidth like Pentium 4's and Xeons and since Montecito is Dual-core, 2 thread per core(it's called Switch on Event Multithreading, which is different from Simultaneous Multithreading which Intel calls Hyperthreading), double the L2 cache of Madison9M's cache and some will be VERY useful.

By the way, Montecito performance figures are 1.5x-2.0x PER core, with same 400MHz bus speed as Madison said here, and is rumored to have a version that's available with 18GB/sec FSB and memory bandwidth, from the current 6.4GB/sec: http://www.realworldtech.com/forums/index.cfm?acti...

Thanks for reading(if you did anyway).

IntelUser2000 - Tuesday, September 14, 2004 - link

JarredWalton - Friday, September 10, 2004 - link

#25 - I think I saw something from AMD that suggested that software should be licensed per socket in the future. Obviously, MS will do what they feel is in their best interest, but license fees per socket would be nice.#23 - There *are* drawbacks to having an integrated memory controller, and Hypertransport probably doesn't boost speed in single processor installations much at all. Anyway, Intel certainly has had some difficulties of late witht their CPU design. What I'm saying, though, is that their manufacturing facilities are probably the best around, with IBM coming in second.

plk21 - Thursday, September 9, 2004 - link

So, how will this affect Microsoft's Per Processor licensing on SQL Server? Will I have to buy 2 licenses per processor? Now I'm running it on Hypertrhreaded chips, only with 1 license per physical chip...PsharkJF - Thursday, September 9, 2004 - link

#21I wasn't saying that Intel's helping them, I'm saying that Intel is being AMD's guinea pig :P

#22

------

One fine day Intel might come back with a vengeance and show us someting that beats the crap out of AMD64

------

Dual pentium M with onboard memory controller *drool*

ceefka - Thursday, September 9, 2004 - link

What puzzles me is, when they are so "ahead of the game", why didn't they too come up with the idea of an onboard mem-controller and something like Hypertransport or Hypertransport itself? If you see what it does for AMD64's and Opterons, imagine what it could do for a Prescott or Xeon. No Sir, they just slap on extra cache, pump the FSB some more and leave the darn thing screaming for bandwith. In my view they are also a little complacent.One fine day Intel might come back with a vengeance and show us someting that beats the crap out of AMD64 or Opteron. That's what I've been thinking for almost 6 months now... If only AMD would sit still for a minute ;-)

JarredWalton - Thursday, September 9, 2004 - link

#21 - Actually, that's not at all correct, unless you think that Intel is sending over their people to help AMD out with getting their 90 nm up and running? IBM might do that, but not Intel. :p AMD is also still using 200 mm wafers, which is seriously behind the state of the art. Basically, AMD started investing in their 90 nm plant 2+ years ago, so they weren't waiting for Intel to have problems and work them out. They're starting construction of a 65 nm plant as well, which will finally get them 300 mm wafers. AMD still makes a great chip, but honestly Intel is ahead on several key areas of manufacturing technology.PsharkJF - Thursday, September 9, 2004 - link

#13------

You can make a case for some issues with their designs of late, but as far as technology? We've seen 90 nm parts from Intel for almost a year now (more if you count early samples), while AMD is only just starting to ship them.

------

In other words, AMD is playing it smart and letting Intel work out the kinks in the technology for them before they spend any money doing things that may not work well.

Also consider that Intel needs smaller dies due to higher clockspeed requirements.

8NP4iN - Wednesday, September 8, 2004 - link

the message is clear

intel has failed

PrinceGaz - Wednesday, September 8, 2004 - link

I dread to guess at just how expensive those Montecito's with 1.7 billion transistors would cost. Probably quite a bit more than the $400 or so I'm looking to spend on my next CPU, I reckon :)