Intel Dual Core Performance Preview Part II: A Deeper Look

by Anand Lal Shimpi on April 6, 2005 12:23 PM EST- Posted in

- CPUs

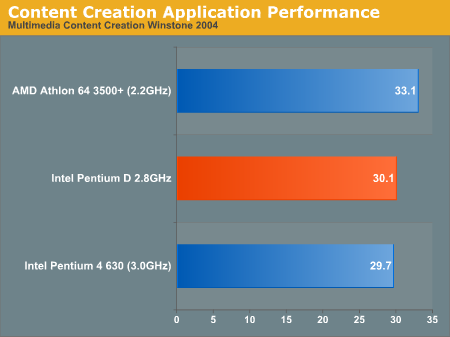

Multimedia Content Creation Performance

MCC Winstone 2004

Multimedia Content Creation Winstone 2004 tests the following applications in various usage scenarios:

- Adobe® Photoshop® 7.0.1

- Adobe® Premiere® 6.50

- Macromedia® Director MX 9.0

- Macromedia® Dreamweaver MX 6.1

- Microsoft® Windows MediaTM Encoder 9 Version 9.00.00.2980

- NewTek's LightWave® 3D 7.5b

- SteinbergTM WaveLabTM 4.0f

All chips were tested with Lightwave set to spawn 4 threads.

Once again, AMD's 3500+ takes the lead in the MCC tests, despite the benefits of dual core in the area.

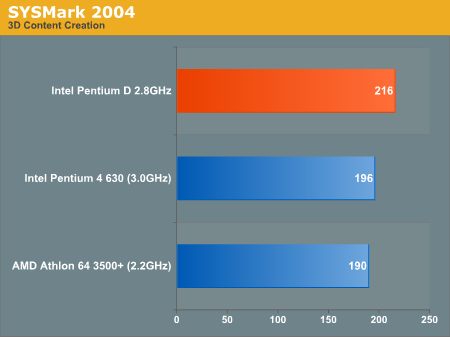

ICC SYSMark 2004

The first category that we will deal with is 3D Content Creation. The tests that make up this benchmark are described below:

"The user renders a 3D model to a bitmap using 3ds max 5.1, while preparing web pages in Dreamweaver MX. Then the user renders a 3D animation in a vector graphics format."

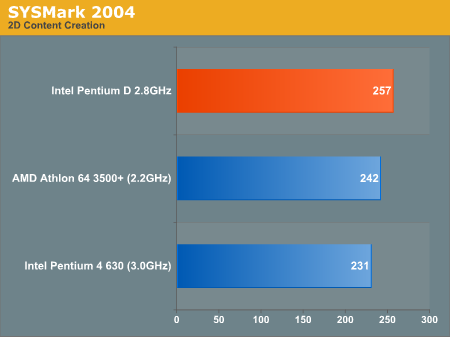

Next, we have 2D Content Creation performance:

"The user uses Premiere 6.5 to create a movie from several raw input movie cuts and sound cuts and starts exporting it. While waiting on this operation, the user imports the rendered image into Photoshop 7.01, modifies it and saves the results. Once the movie is assembled, the user edits it and creates special effects using After Effects 5.5."

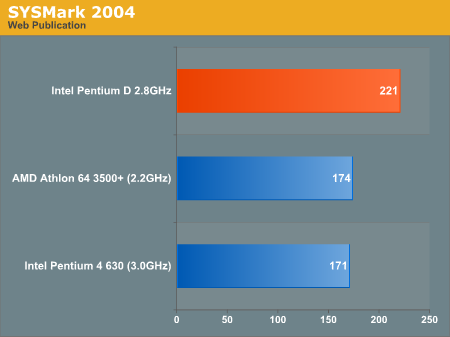

The Internet Content Creation suite is rounded up with a Web Publishing performance test:

"The user extracts content from an archive using WinZip 8.1. Meanwhile, he uses Flash MX to open the exported 3D vector graphics file. He modifies it by including other pictures and optimizes it for faster animation. The final movie with the special effects is then compressed using Windows Media Encoder 9 series in a format that can be broadcast over broadband Internet. The web site is given the final touches in Dreamweaver MX and the system is scanned by VirusScan 7.0."

SYSMark shows the exact opposite with the Pentium D taking the lead in all three of the ICC tests.

106 Comments

View All Comments

BoBOh - Monday, April 11, 2005 - link

Where are the code compile tests. We're not all gamers, some are software developers! :)BoB

NightCrawler - Saturday, April 9, 2005 - link

Dual core Athlon 64's in June ?fitten - Saturday, April 9, 2005 - link

- also, there should be (SMT) after simultaneous multi-threading in the quote from the paper on the IBM site.fitten - Saturday, April 9, 2005 - link

- quote should be in front of "Scalable not after.fitten - Saturday, April 9, 2005 - link

a) By definition, Intel's implementation must be different than IBM's or anyone elses' because the CPUs aren't implemented the same. Not only do they implement different ISAs, but the entire architectures are different... different number of registers, different ISA, different designs.2) Intel's definition of HyperThreading: http://www.intel.com/technology/hyperthread/

D) This paper http://domino.watson.ibm.com/acas/w3www_acas.nsf/i...$FILE/heinrich.pdf , found on IBM's site by searching, is entitled Scalable "Multi-threaded Multiprocessor Architectures". The first paragraph states: "The former [hardware multi-threading], in the form of hyper-threading (HT) or simultaneous multi-threading, appears in the Intel Xeon and Pentium 4, and the IBM POWER5."

Reflex - Friday, April 8, 2005 - link

Well first off, I am not going to do everyone's homework on this, the info is out there, you all have Google. If you ask a IBM engineer if what Intel is doing is the same as what they are doing, or even if it is really SMT, they would tell you flat out that it is not and they fullfill completely different needs in their products and are implemented completely different. Your definition seems to be that the hardware can accept two threads, therefore it is SMT. That is a VERY simplisitic definition of what SMT is, when there are actually many variations on the concept(HT is a variation, but it is not what most CPU engineers consider actual SMT).One of the primary issues here is that HT does not actually allow two simultanious threads, it is more of a enhanced thread scheduler that attempts to fill unused units with jobs that are pending. A true SMT CPU is actually architecturally able to execute two simultanious threads, its not just filling in idle parts of the pipeline with something to do(highly parallel designs). There is a ton of info on this, if you care I suggest you do the research yourself, I don't have the time(and in some ways the expertise) to write a lengthy article on the topic.

Alternatly, you can just buy into the marketing I suppose, its no skin off my teeth.

fitten - Friday, April 8, 2005 - link

I was going to comment on the phrase "true SMT" above. I'm wondering if this comes from the same lines of thought as the "true dual-core" arguments.Anyway, "HyperThreading" (HT) is just Intel marketing terminology for Symmetric MultiThreading (SMT). They are one and the same, with the same design goals... to more effectively utilize core resources by keeping the resources more busy instead of sitting around idle, particularly at the time granularity of cache misses and/or latencies.

defter - Friday, April 8, 2005 - link

#93 "Intel has labeled it as SMT, however there is another name for what they are doing(that I cannot remember at the moment). What they are calling SMT is nowhere even close to solutions like Power."Well please tell us the exact definition of SMT and the difference between the multithreading in Power and P4?

"That aside, the implementation Intel has chosen is designed to make up for inefficiencies in the Prescott pipeline"

In Prescott pipeline? Why did the HT exist in Northwood based Xeons then? Of course the SMT is designed to reduce inefficiencies in the pipeline. If the CPU can utilize most of its resources when running a single thread there isn't a point of implementing SMT.

saratoga - Friday, April 8, 2005 - link

#93: Intel labeled SMT Hyperthreading. It is effectively the same as what the newer Power processors do (make one core two threads wide).It also was not designed for Prescott, rather it was included in the P7 core from the beginning. For this reason it was available on P4s prior to Prescott.

saratoga - Friday, April 8, 2005 - link

#80:HT improves the utilization of execution resources. Its not a bandaid, its a design choice. In some cases it can be used to compensate for some other weakness, in others it can simply be to increase throughput on multithreaded workloads.

Sun and IBM use it because they build server systems and SMT makes a large difference in traditional server loads.

Intel uses it because they realized it would work well with the P4. I don't know why AMD does not use it. Probably because they don't think the Athlon has enough unused hardware on typical loads to justify the extra transistors. Or maybe just because the Athlon was not designed with it in mind and they can't justify redoing the whole thing to add a single feature. Or maybe a combination of the two.