ServerWorks HEsl: DDR bandwidth without DDR SDRAM

by Anand Lal Shimpi on February 7, 2001 8:16 AM EST- Posted in

- CPUs

More PCI bandwidth requires more memory bandwidth

The LE chipset can get away with "only" 1.06GB/s of memory bandwidth since it does not support AGP, leaving your PCI devices and your CPUs as the only users of that bandwidth. But with the HEsl chipset, adding in AGP 2X support stretches the limits of that available memory bandwidth. Since ServerWorks intended the HEsl chipset to be for even more high-end applications, they did take this into account.

The methods for increasing memory bandwidth in regards to the PCI bus are applicable here as well. You can either increase the operating frequency or widen the bus. Increasing the operating frequency of PC133 SDRAM is out of the question since you would have to define an entirely new standard, get support from the memory manufacturers and do all the necessary testing which isn't the easiest thing to do. Widening the bus is a very realistic option and it is the path that ServerWorks chose with the HEsl chipset, but not in the same sense you would think.

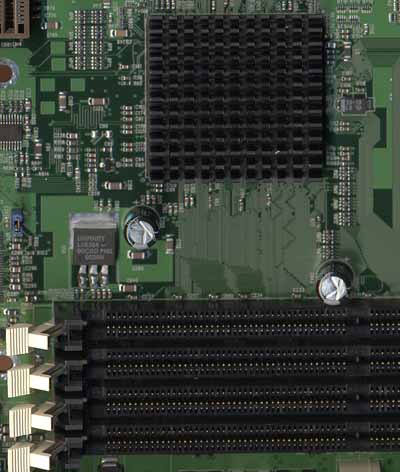

As we know from our chipset reviews in the past, the North Bridge of a chipset houses the memory controller among other things. Normally, this memory controller provides a 64-bit path to the system memory. In the case of the HEsl's North Bridge, there are simply two of these 64-bit paths to the system memory.

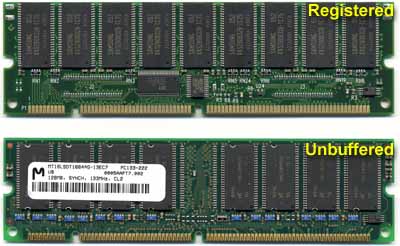

These two "ports" are made possible by ServerWorks' own Memory Address Data Path controller that is integrated into the North Bridge. The two 64-bit ports are interleaved to provide bandwidth similar to what a 128-bit memory bus would while still conforming to the PC133 SDRAM specification. The only stipulation is that you have to install the 64-bit SDRAM modules in pairs (to total the effective 128-bit bus width) and, as is the case with most server solutions, the modules must be Registered and support ECC.

For those of you that aren't familiar with Registered DIMMs, they are not generally the same type of modules you use in your personal systems except for in some unusual cases (you will most likely know if you have registered memory or not). In contrast to unbuffered SDRAM (conventional SDRAM), Registered SDRAM features small registers present between the module's interface and the actual SDRAM chips on the PCB. They are often used to decrease loading and allow for more physical SDRAM devices to be used on a single DIMM.

If you do the math, you'll realize that this interleaved memory bus of the HEsl chipset is exactly equal to the amount of memory bandwidth provided by PC2100 DDR SDRAM while the HEsl only requires PC133 SDRAM (1.06GB/s x 2 = 2.1GB/s).

|

Memory Bandwidth Comparison | ||||||

|

Chipset |

Memory Type |

Max. Theoretical Bandwidth | ||||

|

i815 |

SDRAM |

1.06GB/s | ||||

|

i820 |

RDRAM |

1.6GB/s | ||||

|

i840 |

dual channel RDRAM |

3.2GB/s (2 channels) | ||||

|

Apollo Pro 133A |

SDRAM |

1.06GB/s | ||||

|

Apollo Pro 266 |

DDR SDRAM |

2.1GB/s | ||||

|

ServerSet III HEsl |

SDRAM |

2.1GB/s | ||||

When you take into account that DDR isn't exactly 100% efficient and you don't often get a doubling of the actual memory bandwidth, as well as the fact that regular PC133 SDRAM is still accessed at a lower latency than PC2100 SDRAM, you'll realize that ServerWorks is onto something very special with the HEsl chipset.

To take things even further, on the higher-end quad processor Xeon platforms, ServerWorks has a special version of the HEsl chipset simply called the ServerSet III HE. This chipset uses an external Memory Address Data Path (MADP) controller that provides a total of four x 64-bit interleaved memory ports for an effective 256-bit memory bus and up to 4.1GB/s of available memory bandwidth.

0 Comments

View All Comments