ARM A53/A57/T760 investigated - Samsung Galaxy Note 4 Exynos Review

by Andrei Frumusanu & Ryan Smith on February 10, 2015 7:30 AM EST20nm Manufacturing Process

Both Samsung Semiconductor and TSMC delivered their first 20nm products in Q3 2014, but they don't represent the same jump in efficiency. Samsung's 28nm HKMG process varied a lot from TSMC's 28nm HPM process. While Samsung initially had a process lead with their gate-first approach when introducing 32nm HKMG and subsequently the 28nm shrink, TSMC went the route of gate-last approach. The advantage of the gate-last approach is that it allows for lower variance in the manufacturing process and being able to allow for better power characteristics. We've seen this as TSMC introduced the highly optimized HPM process in mobile. Qualcomm has been the biggest beneficiary as they've taken full advantage of this process jump with the Snapdragon 800 series as they moved from 28nm LP in previous SoCs.

In practical terms, Samsung is brought back on even terms with TSMC in terms of theoretical power consumption. In fact, 28nm HPM still has the same nominal transistor voltage as Samsung's new 20nm process.

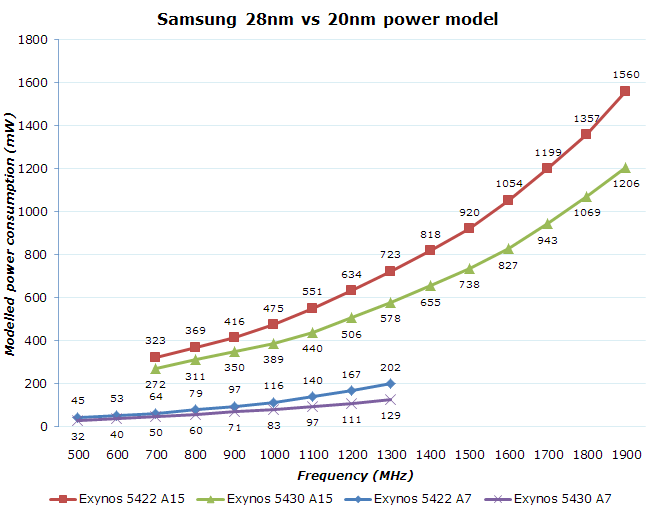

Luckily Samsung provides useful power modeling values as part of the new Intelligent Power Allocation driver for the 5422 and 5430 so we can get a rough theoretical apples-to-apples comparison as to what their 20nm process brings over the 28nm one used in their previous SoCs.

I took the median chip bin for both SoCs to extract the voltage tables in the comparison and used the P=C*f*V² formula to compute the theoretical power figure, just as Samsung does in their IPA driver for the power allocation figures. The C coefficient values are also provided by the platform tables.

We can see that for the A15 cores, there's an average 24% power reduction over all frequencies, with the top frequencies achieving a good 29% reduction. The A7 cores see the biggest overall voltage drop, averaging around -125mV, resulting in an overall 40% power reduction and even 56% at the top frequency. It's also very likely that Samsung has been tweaking the layout of the cores for either power or die size; we've seen this as the block sizes of the CPUs have varied a lot between the 5410, 5420 and 5422, even though they were on the same process node.

While these figures provide quite a significant power reduction by themselves, they must be put into perspective with what Qualcomm is publishing for their Krait cores. The Snapdragon 805 on a median speed bin at 2.65GHz declares itself with a 965mW power consumption, going down to 57mW at 300MHz. While keeping in mind that these figures ignore L2 cache power consumption as Qualcomm feeds this on a dedicated voltage rail, it still gives us a good representation of how efficient the HPM process is. The highest voltages on the S805 are still lower than the top few frequencies found on both the 5430 and the 5433.

20nm does bring with itself a big improvement in die size. If we take the 5420 as the 28nm comparison part and match it against the 5430, we see a big 45% decrease on the A7 core size, and an even bigger 64% reduction on the A15 core size. The total cluster sizes remain relatively conservative in their scaling while shrinking about 15%; this is due to SRAM in the caches having a lower shrinking factor than pure logic blocks. One must keep in mind that auxiliary logic such as PLLs, bus interfaces, and various other small blocks are part of a CPU cluster and may also impact the effective scalability. Samsung also takes advantage of artificially scaling CPU core sizes to control power consumption, so we might not be looking at an apples-to-apples comparison, especially when considering that the 5430 is employing a newer major IP revision of the CPU cores.

| Exynos 5420 vs Exynos 5430 block sizes | ||||

| Exynos 5420 | Exynos 5430 | Scaling Factor | ||

| A7 core | 0.58mm² | 0.4mm² | 0.690 | |

| A7 cluster | 3.8mm² | 3.3mm² | 0.868 | |

| A15 core | 2.74mm² | 1.67mm² | 0.609 | |

| A15 cluster | 16.49mm² | 14.5mm² | 0.879 | |

The Mali T628 between the 5420 and the 5430 actually had an increase in die size despite the process shrink, but this is due to a big increase in the cache sizes.

Samsung regards their 20nm node as very short-lived and the 5430 and 5433 look to be the only high volume chips that will be coming out on the process as their attention is focused on shipping 14nm FinFET devices in the next few months. In fact at the Samsung Investor Forum 2014 they announced mass production of a new high-end SoC has already begun mid-November and will be ramping up to full volume in early 2015. I suspect this to be the Exynos 7420 as that is the successor SoC to the 5433.

All in all, the argument that this 20nm chip should be more power efficient than the competitors' 28nm is not completely factual and doesn't seem to hold up in practice. The process still seems young and unoptimized compared to what TSMC offers on 28nm.

Before we get to the performance and power figures, I'm handing things over to Ryan as we take a look at the architectural changes, starting with an analysis of the Cortex A53.

135 Comments

View All Comments

Sonicadvance1 - Tuesday, February 10, 2015 - link

"The overall increase in cache helps to improve performance, though perhaps more importantly the larger instruction cache helps to offset the larger size of the 64-bit ARM instructions."This is incorrect. AArch64 has a 32bit instruction length just like ARMv7.

Unless of course you were comparing to 16bit Thumb instructions. Vague in either case.

jjj - Tuesday, February 10, 2015 - link

Wish you would have included power numbers for A15 and A7 on 28nm since that's the more common process for A15/A7 and it's unlikely we'll see them much on 20nm and bellow (to be clear, not saying that you should have excluded the numbers on 20nm).Said this before, very curious about the encryption gains in actual use for both power and perf so maybe you guys look at that at some point. And maybe include https sites in the web browsing battery tests- tests that are kinda fuzzy on the methodology, maybe you've detailed it somewhere and i just don't remember.

The process scaling is surprising, maybe TSMC did better,we'll have to see.

Any clue how A53 power scales at much higher clocks, obviously not from this testing. Wondering how it would perform at very high clocks vs a lower clocked A57. At.1.3GHz the A53 seems to use some 3 times less power than A57 and given it's die size if it could go to 2.5Ghz on 20nm it would be interesting, at least from a cost perspective.

Andrei Frumusanu - Tuesday, February 10, 2015 - link

I only have a S4 with an 5410 at disposition, and that is running cluster migration and it's a very old chip by now. The only other candidates would have been the 5422 S5 variant which I don't posses, or to have to destroy the unibody shells of my Huawei devices to be able to do a proper power measurement.I did overclock the A53, but above 1.5GHz it's not worth running the little cores as the voltage rise is too high and the A57's at low frequency are more efficient. This is highly dependent on the core implementation, I imagine MediaTek's SoCs with high clocked "little" cores are much better optimized in such scenarios.

jjj - Tuesday, February 10, 2015 - link

Thanks for the reply.I kinda like the A53 perf at 1.5GHz and above ,nice little core and nice boost for the market it's addressing. In this SoC it does seem that above 900MHz the power goes up a lot.

Devo2007 - Tuesday, February 10, 2015 - link

Interesting to see the PCMark numbers, and how Lollipop seems to help. Given that Lollipop overall "feels" smoother, it makes sense there would be something that would allow that to be somewhat measurable.Running an early build of CM12 on my Snapdragon Note 3, and I'm seeing numbers nearly on-par with the Nexus 5 shown here.

Pissedoffyouth - Tuesday, February 10, 2015 - link

I'm running CM12 on my Note right from from an early Temasek build. Absolutely love it, and there aren't too many showstopping bugs.I hope they do put note 3 on this graph.

Devo2007 - Tuesday, February 10, 2015 - link

Yup! Teamasek 7.5.1 as of today for me (was on 7.4 when I wrote that post). Absolutely loving it now, and feel comfortable using it as my daily driver.Ranger101 - Tuesday, February 10, 2015 - link

This is the most interesting and relevant technical read I have had for some time.An excellent article.

Well done Messrs Frumusanu and Smith.

juicytuna - Tuesday, February 10, 2015 - link

Monster of an article. Will take me many rereads to take it all in.This is what Anandtech is all about, this is what separates it from the rest.serendip - Tuesday, February 10, 2015 - link

Excellent article, I really appreciate the in-depth analyses on the differences between the Exynos and SnapDragon SOCs. I'm shaking my head at Samsung's mad product line though. They seem to make a different variant for each region with so many SOC/modem/RF combinations.Wouldn't it be better to have just one or two variants supporting most of the LTE frequencies out there? I would hate to be the person at Samsung in charge of software updates for these phones. You would need a huge developer team to keep track of per-device changes and fixing bugs while keeping the code consistent along the same model line.