Samsung Announces big.LITTLE MP Support in Exynos 5420

by Brian Klug on September 11, 2013 1:22 AM EST- Posted in

- Smartphones

- Arm

- Exynos

- Mobile

- Tablets

- exynos 5 octa

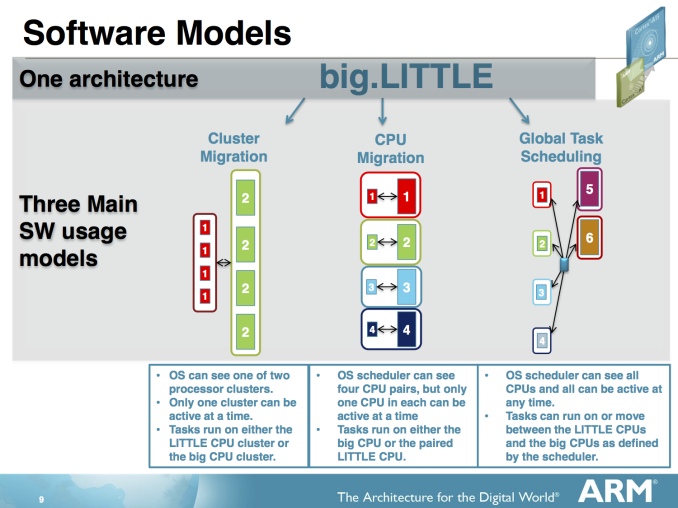

It hasn't been much of a secret in the SoC space that big.LITTLE on the original Exynos 5 Octa (5410) didn't end up working in the most optimal fashion. Instead of using core migration or the Heterogeneous Multi-Processing (HMP) big.LITTLE models, the 5410 instead used cluster migration which meant either all 4 ARM Cortex A15s or 4 ARM Cortex A7s were lit up.

For those not familiar, there are three big.LITTLE models, core switching, in which any of the A7 and A15 cores can be swapped, cluster switching, in which either all A7s or all A15s can be swapped, or HMP, where the kernel is aware of all cores and can schedule threads to any of the cores all at once. This final model is coming to Exynos 5420 by the end of Q4 2013 and will be available to partners shipping product based on its reference platform.

ARM gave us a chance to take a look at the HMP enabled Exynos 5420 reference platform running through a few demos, showing the kernel swapping in and out A7s and A15 cores as system workload changed. I got to see these in person but ARM has also posted them on YouTube in quality better than I could've captured.

Exynos 5420 also includes the necessary fixes to the cache coherency interface (CCI-400) that enable it to work this time between the A7s, A15s, and Mali T-628, versus 5410 which didn't enable it and thus suffered loss of efficiency. This makes 5420 the first real platform to take a look at the full promise of ARM's big.LITTLE model.

Source: Samsung

30 Comments

View All Comments

Kenan_sadhu - Wednesday, September 11, 2013 - link

This is what I want to ask too. So early in its life, note 3 and the new note 10.1 won't have this, and it will be enabled by software? Or, god forbid, the next revision will have this, hardware-wise, anf the early adopters are screwed?tuxRoller - Wednesday, September 11, 2013 - link

It shouldn't require any other than big.LITTLE. Even the CCI is intended more for the older, hypervisor driven core migration (but, I'd imagine, it would come in use when migrating tasks, but with since we are doing aSMP I'd expect you'd see less of that). With this the new scheduler the system should be seen as a sort of weird 8 core cpu mixed with a cluster.jjj - Wednesday, September 11, 2013 - link

Makes me curious about how 2xA15 + 4xA7 would do.mmrezaie - Wednesday, September 11, 2013 - link

I was thinking about the same thing, but I suppose Snapdragon's solution is better when you can just play with the voltage on just four cores.HisDivineOrder - Wednesday, September 11, 2013 - link

Seems like you'd have either low performance required scenarios that need only a few low performance cores or high performance scenarios where you need lots of high performance ones.Why would you ever want lots of low performance cores and few high performance cores?

jjj - Wednesday, September 11, 2013 - link

For lower power/heat and smaller die(smaller is cheaper). If you looked at the videos you don't have all 4 A15 at peak all that much and with only 2 A15 you can clock them higher.Anyway, i wasn't hoping for such SoC, it's a known fact we'll get some, just curious about perf and power since it might be a very solid combination.

willstay - Wednesday, September 11, 2013 - link

I thought Exynos 5420 was coming to Note 3 Intl version. End of Q4 is December and Note 3 is releasing this Sept 25. I suddenly don't want to buy Note 3 given that I want latest cpu. It is bad in the part of Samsung to release this news just at the verge of releasing flagship phone.boris81 - Wednesday, September 11, 2013 - link

I'm confused too.The way I understood it from reading GSMarena is that GS4 has Exynos 5410 with Cluster Migration, Note3 has Exynos 5420 with CPU Migration and that another Exynos is coming later this year (possibly 5430) with Global Task Scheduling.

-

phoenix_rizzen - Wednesday, September 11, 2013 - link

I don't understand the need for HMP in a phone, or even a tablet. Core migration makes sense (the OS only sees 4 CPU cores, the SoC switches between the A7 or A15 as needed on a per-Core basis). IOW, the system would be using one of the following setups, depending on the load:- 4x A7 + 0x A15

- 3x A7 + 1x A15

- 2x A7 + 2x A15

- 1x A7 + 3x A15

- 0x A7 + 4x A15

That setup makes sense to me, and can be done all in hardware. HMP doesn't; sounds like a lot of extra complexity and scheduler "magic" to make it work, and lots of ways to make it not work.

frenchy_2001 - Wednesday, September 11, 2013 - link

The goal is to allow more flexible configurations, like 4xA7+2xA15 or the next Tegra with 4xA15 and 2xA7 for power reduction (instead of 5xA15).This should allow for both better instant power and lower idle/low usage power, while keeping area under control (A7 is MUCH smaller than A15). Very powerful for the future.

I hope we will see more of those and I'm sure we'll find great new combinations for the best overall experience.