Intel Iris Pro 5200 Graphics Review: Core i7-4950HQ Tested

by Anand Lal Shimpi on June 1, 2013 10:01 AM EST

The Prelude

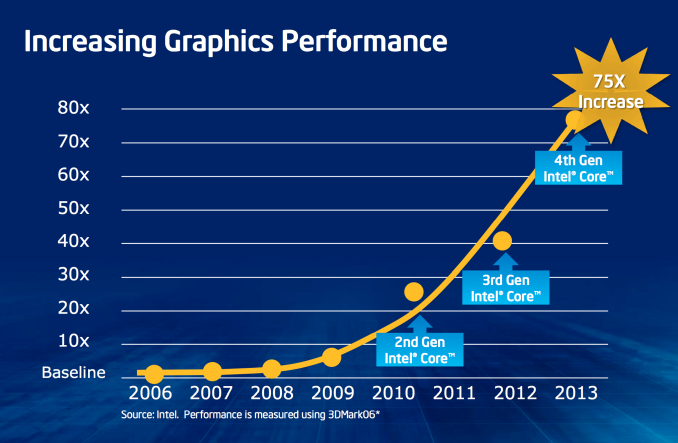

As Intel got into the chipset business it quickly found itself faced with an interesting problem. As the number of supported IO interfaces increased (back then we were talking about things like AGP, FSB), the size of the North Bridge die had to increase in order to accommodate all of the external facing IO. Eventually Intel ended up in a situation where IO dictated a minimum die area for the chipset, but the actual controllers driving that IO didn’t need all of that die area. Intel effectively had some free space on its North Bridge die to do whatever it wanted with. In the late 90s Micron saw this problem and contemplating throwing some L3 cache onto its North Bridges. Intel’s solution was to give graphics away for free.

The budget for Intel graphics was always whatever free space remained once all other necessary controllers in the North Bridge were accounted for. As a result, Intel’s integrated graphics was never particularly good. Intel didn’t care about graphics, it just had some free space on a necessary piece of silicon and decided to do something with it. High performance GPUs need lots of transistors, something Intel would never give its graphics architects - they only got the bare minimum. It also didn’t make sense to focus on things like driver optimizations and image quality. Investing in people and infrastructure to support something you’re giving away for free never made a lot of sense.

Intel hired some very passionate graphics engineers, who always petitioned Intel management to give them more die area to work with, but the answer always came back no. Intel was a pure blooded CPU company, and the GPU industry wasn’t interesting enough at the time. Intel’s GPU leadership needed another approach.

A few years ago they got that break. Once again, it had to do with IO demands on chipset die area. Intel’s chipsets were always built on a n-1 or n-2 process. If Intel was building a 45nm CPU, the chipset would be built on 65nm or 90nm. This waterfall effect allowed Intel to help get more mileage out of its older fabs, which made the accountants at Intel quite happy as those $2 - $3B buildings are painfully useless once obsolete. As the PC industry grew, so did shipments of Intel chipsets. Each Intel CPU sold needed at least one other Intel chip built on a previous generation node. Interface widths as well as the number of IOs required on chipsets continued to increase, driving chipset die areas up once again. This time however, the problem wasn’t as easy to deal with as giving the graphics guys more die area to work with. Looking at demand for Intel chipsets, and the increasing die area, it became clear that one of two things had to happen: Intel would either have to build more fabs on older process nodes to keep up with demand, or Intel would have to integrate parts of the chipset into the CPU.

Not wanting to invest in older fab technology, Intel management green-lit the second option: to move the Graphics and Memory Controller Hub onto the CPU die. All that would remain off-die would be a lightweight IO controller for things like SATA and USB. PCIe, the memory controller, and graphics would all move onto the CPU package, and then eventually share the same die with the CPU cores.

Pure economics and an unwillingness to invest in older fabs made the GPU a first class citizen in Intel silicon terms, but Intel management still didn’t have the motivation to dedicate more die area to the GPU. That encouragement would come externally, from Apple.

Looking at the past few years of Apple products, you’ll recognize one common thread: Apple as a company values GPU performance. As a small customer of Intel’s, Apple’s GPU desires didn’t really matter, but as Apple grew, so did its influence within Intel. With every microprocessor generation, Intel talks to its major customers and uses their input to help shape the designs. There’s no sense in building silicon that no one wants to buy, so Intel engages its customers and rolls their feedback into silicon. Apple eventually got to the point where it was buying enough high-margin Intel silicon to influence Intel’s roadmap. That’s how we got Intel’s HD 3000. And that’s how we got here.

177 Comments

View All Comments

whyso - Saturday, June 1, 2013 - link

They are completely different systems making power consumption values irrelevant.codedivine - Saturday, June 1, 2013 - link

Hi folks. Can you post the OpenCL extensions supported? You can use something like "GPU Caps viewer" from Geeks3d.tipoo - Saturday, June 1, 2013 - link

Interesting that the compute is punches above it's game performance weight. I wonder if they could put more EUs in a chip, maybe a larger eDRAM, and put it on a board as a compute card.lmcd - Saturday, June 1, 2013 - link

They already have a compute card called Xeon Phi if I remember correctly.Klimax - Sunday, June 2, 2013 - link

Different Arch (X86 in Phi)tipoo - Sunday, June 2, 2013 - link

I'm aware, but the Xeon Phi requires completely different programming than a GPU like this which can just use OpenCL.Soul_Master - Saturday, June 1, 2013 - link

What's your point for comparing desktop GPU with middle-range mobile GPU? CPU on both devices are not equal.Soul_Master - Saturday, June 1, 2013 - link

Sorry. I misunderstood about i7 4950HQ process, a high-end quad-core processor for laptops.Ryan Smith - Sunday, June 2, 2013 - link

It's what we had available. We wanted to test a DDR3 version of GK107, and that's what was on-hand.tipoo - Saturday, June 1, 2013 - link

Hmm, so it's heavily hinted at that the next rMBP will ditch discreet graphics. The 5200 is good, but that would still be a regression in performance. Not the first time Apple would have done that, there was the Radeon cut out of the Mini, the 320M to the 3000, even the bottom rung of the newest iMac with the 640m. I wonder if it would at least be cheaper to make up for it.