Intel's Haswell Architecture Analyzed: Building a New PC and a New Intel

by Anand Lal Shimpi on October 5, 2012 2:45 AM ESTPlatform Retargeting

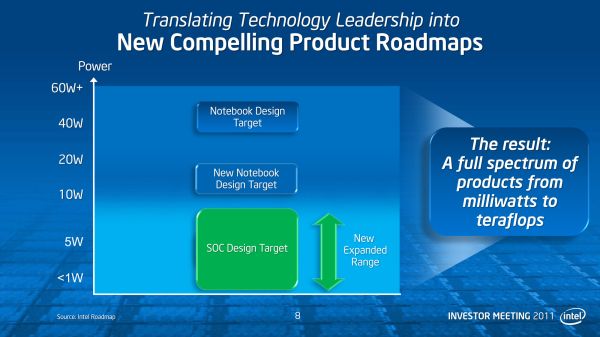

Since the introduction of Conroe/Merom back in 2006 Intel has been prioritizing notebooks for the majority of its processor designs. The TDP target for these architectures was set around 35 - 45W. Higher and lower TDPs were hit by binning and scaling voltage. The rule of thumb is a single architecture can efficiently cover an order of magnitude of TDPs. In the case of these architectures we saw them scale all the way up to 130W and all the way down to 17W.

In the middle of 2011 Intel announced its Ultrabook initiative, and at the same time mentioned that Haswell would shift Intel's notebook design target from 35 - 45W down to 10 - 20W.

At the time I didn't think too much about the new design target, but everything makes a lot more sense now. This isn't a "simple" architectural shift, it's a complete rethinking of how Intel approaches platform design. More importantly than Haswell's 10 - 20W design point, is the new expanded SoC design target. I'll get to the second part shortly.

Platform Power

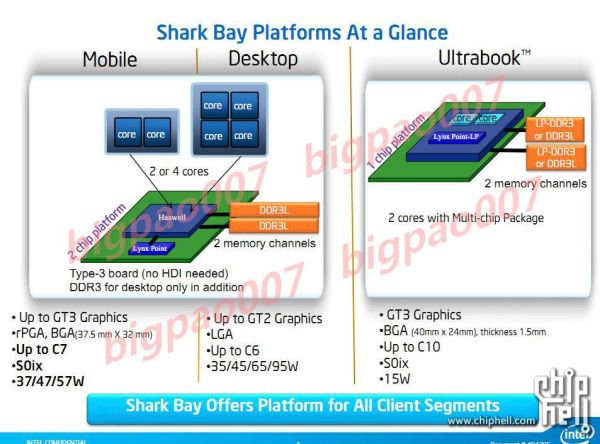

There will be four client focused categories of Haswell, and I can only talk about three of them now. There are the standard voltage desktop parts, the mobile parts and the ultra-mobile parts: Haswell, Haswell M and Haswell U. There's a fourth category of Haswell that may happen but a lot is still up in the air on that line.

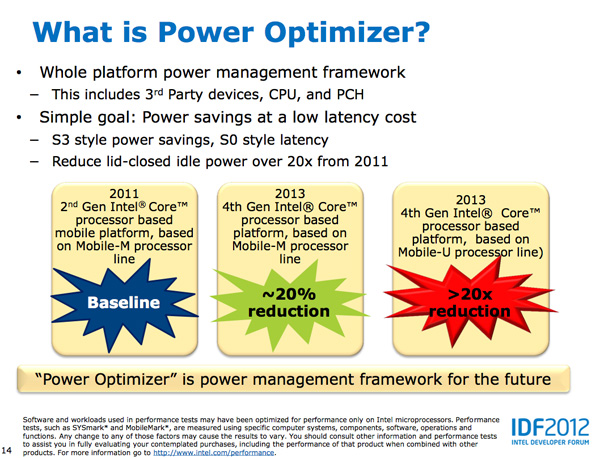

Of the three that Intel is talking about now, the first two (Haswell/Haswell M) don't do anything revolutionary on the platform power side. Intel is promising around a 20% reduction in platform power compared to Sandy Bridge, but not the order of magnitude improvement it promised at IDF. These platforms are still two-chip solutions with the SoC and a secondary IO chip similar to what we have today with Ivy Bridge + PCH.

It's the Haswell U/ULT parts that brings about the dramatic change. These will be a single chip solution, with part of the voltage regulation typically found on motherboards moved onto the chip's package instead. There will still be some VR components on the motherboard as far as I can tell, it's the specifics that are lacking at this point (which seems to be much of the theme of this year's IDF).

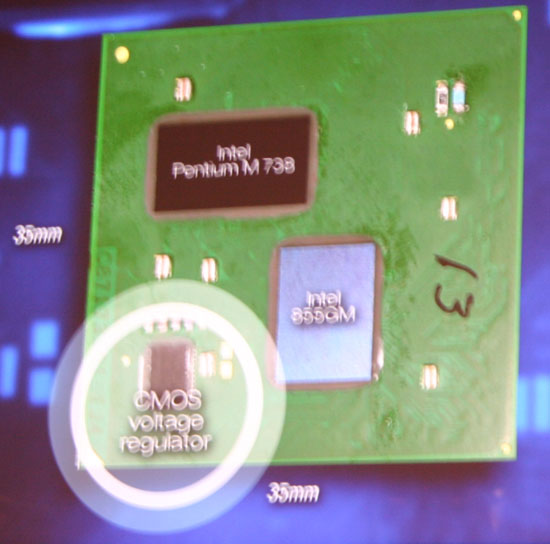

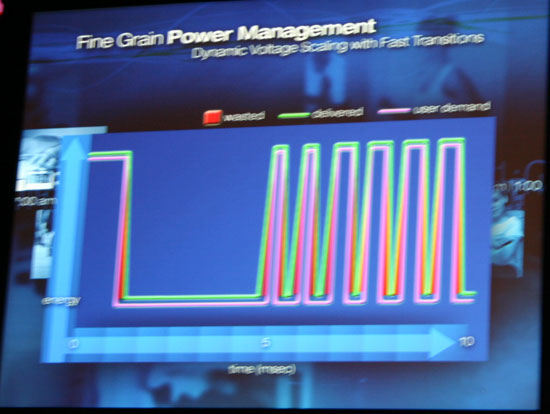

Seven years ago Intel first demonstrated working silicon with an on-chip North Bridge (now commonplace) and on-package CMOS voltage regulation:

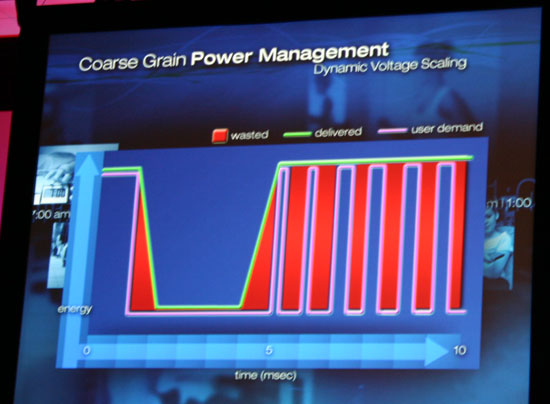

The benefits were two-fold: 1) Intel could manage fine grained voltage regulation with very fast transition times and 2) a tangible reduction in board component count.

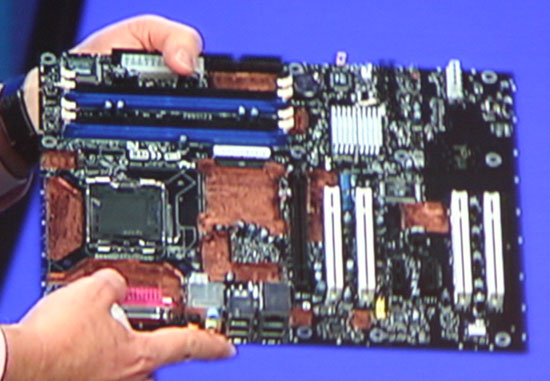

2005 - A prototype motherboard using the technology. Note the lack of voltage regulators on the motherboard and the missing GMCH (North Bridge) chip.

The second benefit is very easy to understand from a mobile perspective. Fewer components on a motherboard means smaller form factors and/or more room for other things (e.g. larger battery volume via a reduction in PCB size).

The first benefit made a lot of sense at the time when Intel introduced it, but it makes even more sense when you consider the most dramatic change to Haswell: support for S0ix active idle.

245 Comments

View All Comments

random2 - Saturday, October 6, 2012 - link

"The race to the bottom that we've seen in the LCD space made it unlikely that any of the panel vendors would be jumping at the opportunity to make their products more expensive."It's unfortunate, because of what might have been had the manufacturers, of which there are only three main ones, if I recall, had the foresight to market to customers that weren't just looking to buy the lowest priced panel on display at Best Buy. Had they the initiative to have started years ago, there would be some pretty fantastic panels available today for much more reasonable prices than seen for the 27 and 30 inch 2560X1600 panels today.

Klugfan - Saturday, October 6, 2012 - link

This doesn't really belong in the Haswell article, but I would love to know more about the physics and constraints of TDP. Like, hit me with a chart of TDP impact for a variety of important parts in phones, tablets, laptops, and desktops. Show me a chart of TDP budgets and mitigation strategies. Explain to me roughly how physics forces those things to relate. Please.Seems important and it's easy to understand the comparison from Ivy Bridge to Haswell but that doesn't feel like the big picture.

havoti97 - Saturday, October 6, 2012 - link

I read the 1st page then got bored. Writing style is overly wordy... am I the only the feeling this way?xeizo - Saturday, October 6, 2012 - link

It's an article, not a twitter feed! Some of us like to get the whole picture not just the flashy stuff ....watersb - Saturday, October 6, 2012 - link

Phenomenal feature, Anand! This is why I check your site each day. Thanks very much!bill4 - Saturday, October 6, 2012 - link

like atom, you're stuck in no mans land. way too high for tablets and phones, but in desktops and laptop, who cares if the amd solution uses 30 watts instead of 8? that difference isn't enough to matter when you take the whole platform into account, especially at lower price points where battery life wont be fantastic anyway. on the dsktop it's completely pointless.JlHADJOE - Sunday, October 7, 2012 - link

On a laptop using 30 watts instead of 8 will more than triple your battery life, especially at lower price points/smaller form factors where manufacturers gimp the battery.How's about browsing for 9 hours instead of 3? Or 27 hours instead of 9? I'd jump on it in a heartbeat.

1008anan - Saturday, October 6, 2012 - link

Haswell will sport 32 single precision or 16 double precision flops per cycle per core for its desktop and high tdp mobile skews [at least 30 watt and up].Can anyone speculate on how many single precision and double precision flops per cycle per core Haswell will execute for its low TDP skews? For example the less than 10 watt skews? the 15 watt skews?

I would also be interested in learning speculation about how many execution units (or shader cores if you prefer standard nomenclature) the low TDP Haswell products will have.

1008anan - Saturday, October 6, 2012 - link

Haswell will be able to execute 16 double precision or 32 single precision flops per clock per core for desktop and high TDP mobile skews [at least 30 watts and up].Can anyone speculate on how many flops per cycle per core the sub 10 watt and 15 watt Haswell skews will execute? Similarly I would be interested in hearing speculation about how many graphic execution units (shader cores) the sub 10 watt and 15 watt Haswell products will come with. Any speculation on graphics clock speed?

Is it possible that the high end tock 22 nm Xeon server parts could have 32 double precision or 64 single precision flops per clock per core?

Laststop311 - Saturday, October 6, 2012 - link

Best explanation of haswell I've read to date. Good Job Anand.