Intel's Haswell Architecture Analyzed: Building a New PC and a New Intel

by Anand Lal Shimpi on October 5, 2012 2:45 AM ESTPlatform Retargeting

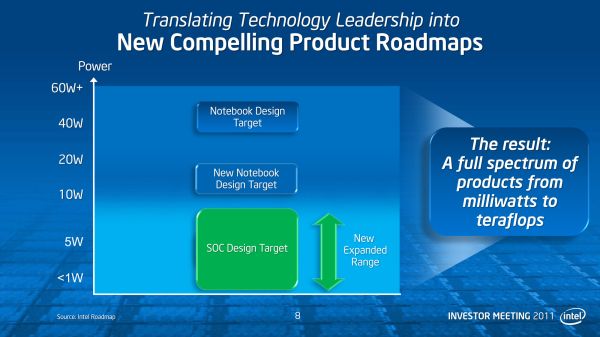

Since the introduction of Conroe/Merom back in 2006 Intel has been prioritizing notebooks for the majority of its processor designs. The TDP target for these architectures was set around 35 - 45W. Higher and lower TDPs were hit by binning and scaling voltage. The rule of thumb is a single architecture can efficiently cover an order of magnitude of TDPs. In the case of these architectures we saw them scale all the way up to 130W and all the way down to 17W.

In the middle of 2011 Intel announced its Ultrabook initiative, and at the same time mentioned that Haswell would shift Intel's notebook design target from 35 - 45W down to 10 - 20W.

At the time I didn't think too much about the new design target, but everything makes a lot more sense now. This isn't a "simple" architectural shift, it's a complete rethinking of how Intel approaches platform design. More importantly than Haswell's 10 - 20W design point, is the new expanded SoC design target. I'll get to the second part shortly.

Platform Power

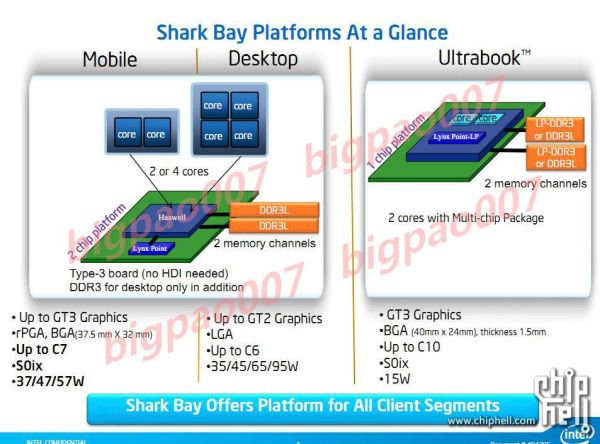

There will be four client focused categories of Haswell, and I can only talk about three of them now. There are the standard voltage desktop parts, the mobile parts and the ultra-mobile parts: Haswell, Haswell M and Haswell U. There's a fourth category of Haswell that may happen but a lot is still up in the air on that line.

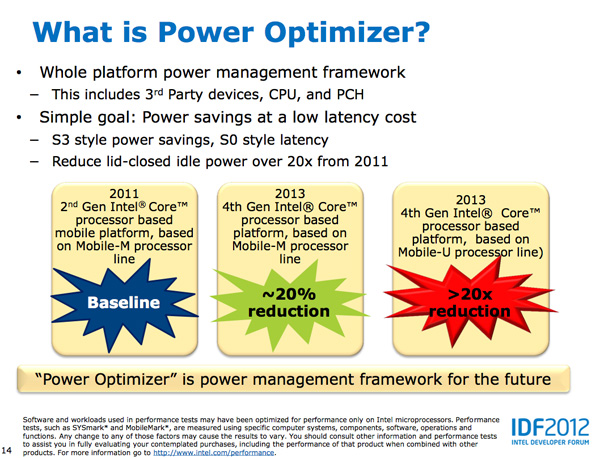

Of the three that Intel is talking about now, the first two (Haswell/Haswell M) don't do anything revolutionary on the platform power side. Intel is promising around a 20% reduction in platform power compared to Sandy Bridge, but not the order of magnitude improvement it promised at IDF. These platforms are still two-chip solutions with the SoC and a secondary IO chip similar to what we have today with Ivy Bridge + PCH.

It's the Haswell U/ULT parts that brings about the dramatic change. These will be a single chip solution, with part of the voltage regulation typically found on motherboards moved onto the chip's package instead. There will still be some VR components on the motherboard as far as I can tell, it's the specifics that are lacking at this point (which seems to be much of the theme of this year's IDF).

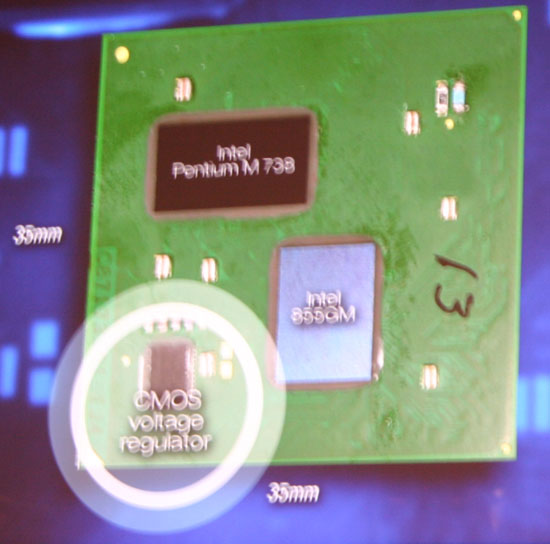

Seven years ago Intel first demonstrated working silicon with an on-chip North Bridge (now commonplace) and on-package CMOS voltage regulation:

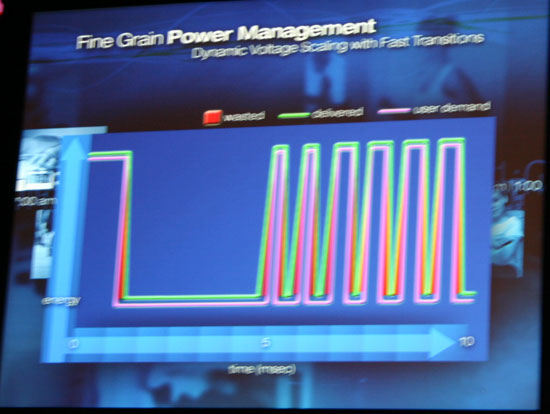

The benefits were two-fold: 1) Intel could manage fine grained voltage regulation with very fast transition times and 2) a tangible reduction in board component count.

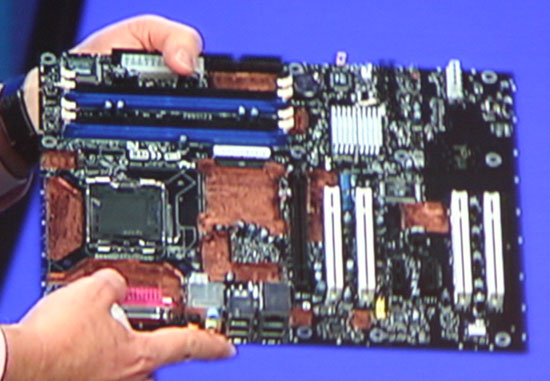

2005 - A prototype motherboard using the technology. Note the lack of voltage regulators on the motherboard and the missing GMCH (North Bridge) chip.

The second benefit is very easy to understand from a mobile perspective. Fewer components on a motherboard means smaller form factors and/or more room for other things (e.g. larger battery volume via a reduction in PCB size).

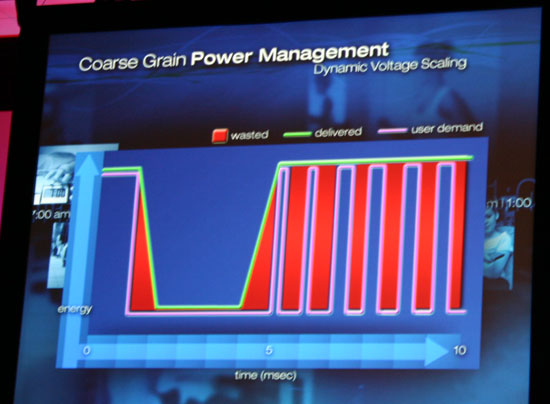

The first benefit made a lot of sense at the time when Intel introduced it, but it makes even more sense when you consider the most dramatic change to Haswell: support for S0ix active idle.

245 Comments

View All Comments

Kevin G - Saturday, October 6, 2012 - link

Losing just the MacBook AIr isn't going to hurt Intel much as a whole but it is doubtful that Apple would just move that product line to ARM. The rest of the line up would likely follow. The results by the numbers would hurt Intel but nothing to doom the company. Intel does have the rest of the PC industry to fall back upon... except the PC market is shrinking.Apple is one of Intel's best gateway into the ultra mobile market. Apple has made indications that they want to merge iOS and OS X over the long term which would likely result in dropping either ARM or x86 hardware to simplify the line up.

WinRT is also a threat to Intel and

Kevin G - Saturday, October 6, 2012 - link

(Hrm... got cut off there)WinRT is also a threat to Intel but WinRT has next to zero market share. The threat here is any success it obtains. Apple on the other hand controls ~75% of the tablet market last I checked.

Andriod is a bit neutral to Intel as manufacturers can transition between ARM and x86 versions with relative ease. Intel will just have to offer competitive hardware at competitive prices here. The sub 10W Haswell parts are going to be competitive but price is a great unknown. The ARM SoC's are far cheaper than what Intel has traditionally been comfortable with. So even if Intel were to acquire all of the Android tablet market, it would be a minority at this time and over the short term (even in the best case scenario, it'd take time for Android based tablets to surpass the iPad in terms of market share).

So ultimately it would be best for Intel to snag Apple's support due to their dominant market share in the tablet space and influential position in the smart phone space.

andrewaggb - Friday, October 5, 2012 - link

Agree with others. Best Anandtech article I've read in a long time.Most articles lack the detail and insights that this one has.

mrdude - Friday, October 5, 2012 - link

Great article. Great depth, great info and very thorough. Hats off :)But I couldn't shake the feeling that I was missing perhaps the most important bit of information: price.

Obviously, Intel isn't going to give that away 9 months away from the presumed launch date -- though in typical fashion we'll see it leaked early. It still is the biggest question regarding Haswell's, and in turn Intel's, success against ARM.

I think most consumers are already at that good enough stage, where your Tegra 3 or Snapdragon S4 can fulfill all of their computing needs on a tablet or a phone. The biggest drawback for productivity purposes isn't necessarily the "lack of CPU performance" but rather the lack of a proper keyboard/mouse, gaming, along with a rare application or two that's still locked to x86 (Office rings a bell, though not for long). Or I should say, these were drawbacks. Not any longer.

So is Intel going to cut their margins and go for volume? Or are they just going to keep their massive margins and price themselves out of contention? Apple carries with itself a brand name that people want. It's become more than a gadget but a fashion accessory. People don't mind paying for Apple tax. I don't think I ever will, but at least I can notice the trend. The Intel brand doesn't carry with it the same cult following and neither does x86. Unless Intel is willing to compete with ARM on price, lowering the cost of their products below Apple's, I don't think think the substantial increases in efficiency and performance will matter all that much.

name99 - Friday, October 5, 2012 - link

"Sandy Bridge made ports 2 & 3 equal class citizens, with both capable of being used for load or store address calculation. In the past you could only do loads on port 2 and store addresses on port 3. Sandy Bridge's flexibility did a lot for load heavy code, which is quite common. Haswell's dedicated store address port should help in mixed workloads with lots of loads and stores."The rule of thumb numbers are, on "ordinary" integer type code:

1/6 instructions are branches

1/6 are writes

2/6 are reads

2/6 are ALU

This makes it more obvious why Intel moved as it did.

You want to sustain as close to 4ops/cycle as you can.

This means that your order of adding abilities should be exactly as Intel has done

- first two ALUs

- next two read/writes per cycle (ideal would be a mix of load/store) but Intel gave us that you can do a load+store per cycle

- next two loads per cycle

- next make sure the branches aren't throttled (because back-to-back branches are common, and you want branches resolved ASAP)

- next make the load-store system wide enough to sustain a MAC per cycle (two loads+store)

It's hard to see what is left to complain about at this level.

And of course we have better lock performance. So what's left?

What I think still have substantial room for improvement (correct me if I'm wrong) is

(a) TLB coverage

(b) TLB efficiency.

TLB coverage could be improved with a 2nd level TLB but (as far as I know) Intel doesn't go in for that, unlike POWER.

By TLB efficiency, I mean not needing to lose performance due to different address spaces. Unfortunately Intel seems screwed here. The POWER segment scheme (especially the 64-bit scheme) is REALLY powerful here in allowing multiple address spaces to coexist, so that multiple shared libraries, the main app code, IO, and memory mapped files, can all have persistent simultaneous TLB entries. (Note that this has nothing to do with the Intel segment scheme --- different technology, to solve a different problem.)

As far as I know, right now all Intel has is a single ASID representing a process. Better than no ASID, and having to flush the TLB on every context switch; but not especially good at sharing entries --- so (again as far as I know) shared libraries or shared mem-mapped files being used by multiple processes, even when they are mapped to the same address, have to have separate TLB entries, each one with a different ASID corresponding to the process calling them.

name99 - Friday, October 5, 2012 - link

Stupid me. I should have read the entire article. So we do have a (nicely sized 2nd level TLB).I guess my only remaining complaint now is that ASIDs are too coarse a tool.

In principle you could get dove some of the problems I mention using dedicated large pages for some particular purposes (eg to over the OS code and data, the equivalent of the frame buffer for modern windowing systems, and some pool of common shared libraries).

Does anyone know the extent to which both Windows and OSX actually make use of dedicated large pages in this way?

Peanutsrevenge - Friday, October 5, 2012 - link

Great article Anand, but when will Anand cloning be incorporated in CPU designs so we can all have one of you at home to pull out and extract information from @ will ? ?Although, with that said, I was already made aware of much of this recently from listening in to some random guys babbling about tech stuff on a podcast ;)

Rectified - Friday, October 5, 2012 - link

Anand, you write the best tech articles on the web. As a graduate student in computer engineering, I appreciate the practical yet technical analyses you write on the industry. Keep it up!Crazy1 - Friday, October 5, 2012 - link

I like the concept of Panel Self Refresh, yet I feel that Intel could implement this themselves. I'm not an expert, but couldn't a buffer be placed on the CPU package between the GPU and panel? This may not be as efficient as if the panel makers did it themselves and it would probably only work when using the IGP (when it would most likely have the greatest impact), but at least it is a step in the right direction.Additionally, Great Article! Anandtech provides some of the most thorough technology articles. Keep it up.

random2 - Saturday, October 6, 2012 - link

" If all mainstream client computing moves to smartphones,..........."Seriously? The idea of all mainstream computing done on nothing but smartphones seems to stretch the imagination just a bit much. There isn't even the most basic of businesses that do not have a computer (made with mainstream components as are most small and medium sized businesses) and business software. Don't forget the PC gamers and people who like larger viewing and typing surfaces. Or the fact that in eight years, home and business PC's will be blindingly fast with larger displays with much greater pixel density, possibly clear screen touch surfaces, likely alternative interfaces than just a keyboard and mouse and incredible computing and rendering power.

The likelihood of the general populace turning all their computing needs over to a palm size PC I see as kind of weird fantasy where people learn to love minute typing interfaces and squinting at hi density displays fit into 3.5by 4.5 inches for long periods of the day without interruption. No, to push the idea of micro computing one must discount all of the other advances in the computer/electronics industries in order to make their pet theory viable.