Intel's Haswell Architecture Analyzed: Building a New PC and a New Intel

by Anand Lal Shimpi on October 5, 2012 2:45 AM ESTPlatform Retargeting

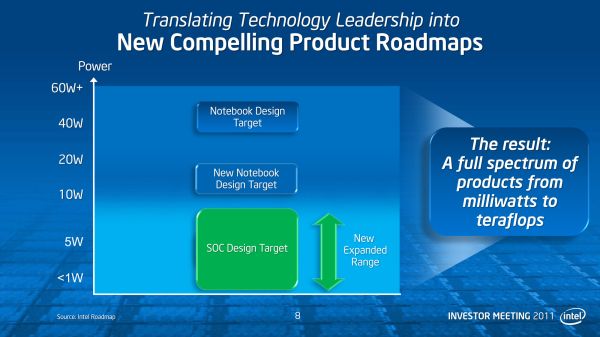

Since the introduction of Conroe/Merom back in 2006 Intel has been prioritizing notebooks for the majority of its processor designs. The TDP target for these architectures was set around 35 - 45W. Higher and lower TDPs were hit by binning and scaling voltage. The rule of thumb is a single architecture can efficiently cover an order of magnitude of TDPs. In the case of these architectures we saw them scale all the way up to 130W and all the way down to 17W.

In the middle of 2011 Intel announced its Ultrabook initiative, and at the same time mentioned that Haswell would shift Intel's notebook design target from 35 - 45W down to 10 - 20W.

At the time I didn't think too much about the new design target, but everything makes a lot more sense now. This isn't a "simple" architectural shift, it's a complete rethinking of how Intel approaches platform design. More importantly than Haswell's 10 - 20W design point, is the new expanded SoC design target. I'll get to the second part shortly.

Platform Power

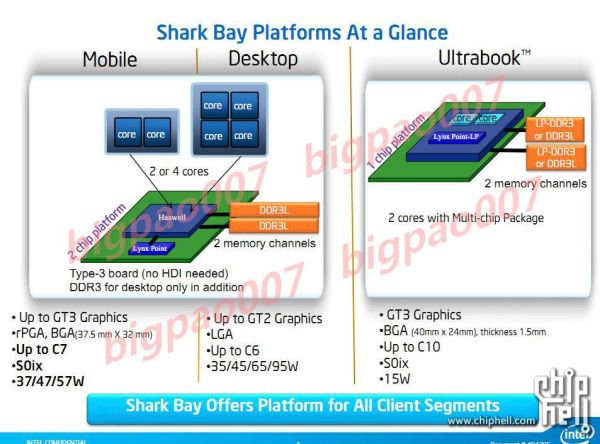

There will be four client focused categories of Haswell, and I can only talk about three of them now. There are the standard voltage desktop parts, the mobile parts and the ultra-mobile parts: Haswell, Haswell M and Haswell U. There's a fourth category of Haswell that may happen but a lot is still up in the air on that line.

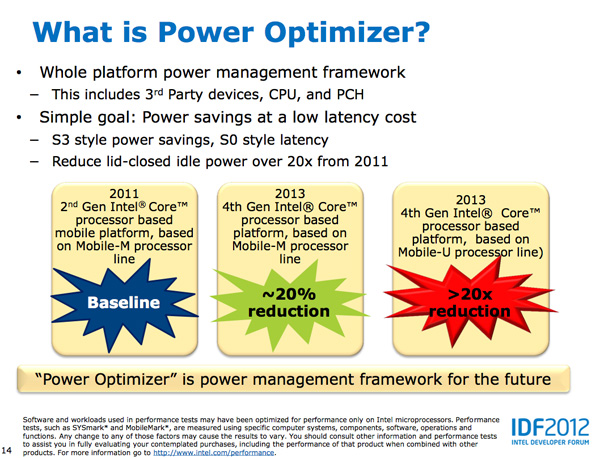

Of the three that Intel is talking about now, the first two (Haswell/Haswell M) don't do anything revolutionary on the platform power side. Intel is promising around a 20% reduction in platform power compared to Sandy Bridge, but not the order of magnitude improvement it promised at IDF. These platforms are still two-chip solutions with the SoC and a secondary IO chip similar to what we have today with Ivy Bridge + PCH.

It's the Haswell U/ULT parts that brings about the dramatic change. These will be a single chip solution, with part of the voltage regulation typically found on motherboards moved onto the chip's package instead. There will still be some VR components on the motherboard as far as I can tell, it's the specifics that are lacking at this point (which seems to be much of the theme of this year's IDF).

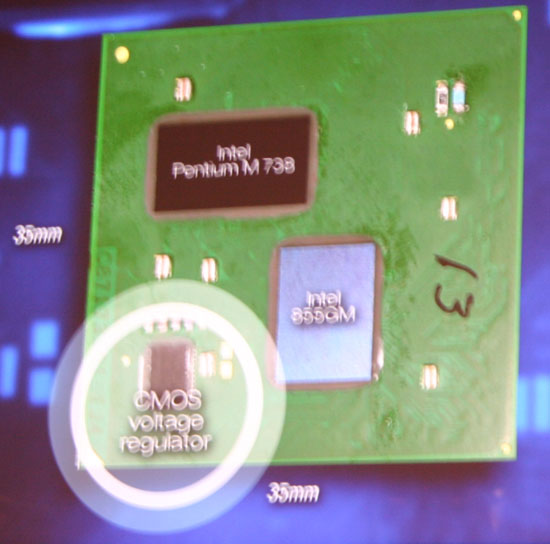

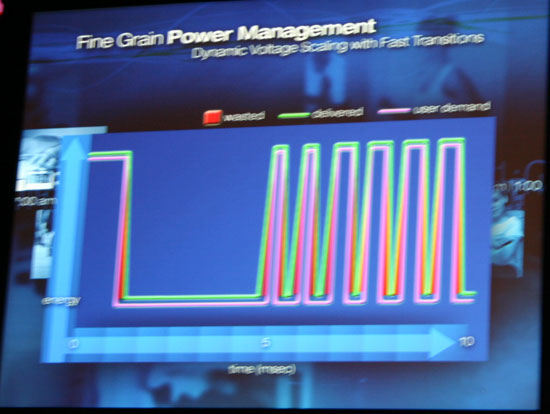

Seven years ago Intel first demonstrated working silicon with an on-chip North Bridge (now commonplace) and on-package CMOS voltage regulation:

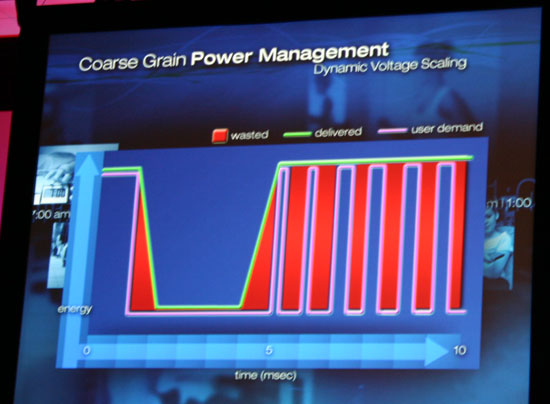

The benefits were two-fold: 1) Intel could manage fine grained voltage regulation with very fast transition times and 2) a tangible reduction in board component count.

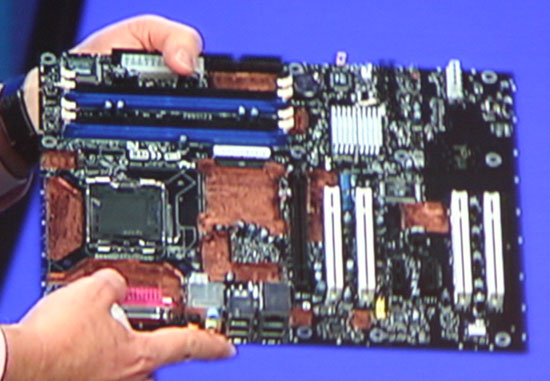

2005 - A prototype motherboard using the technology. Note the lack of voltage regulators on the motherboard and the missing GMCH (North Bridge) chip.

The second benefit is very easy to understand from a mobile perspective. Fewer components on a motherboard means smaller form factors and/or more room for other things (e.g. larger battery volume via a reduction in PCB size).

The first benefit made a lot of sense at the time when Intel introduced it, but it makes even more sense when you consider the most dramatic change to Haswell: support for S0ix active idle.

245 Comments

View All Comments

tipoo - Sunday, October 7, 2012 - link

I don't think so, doesn't the HD4000 have more bandwidth to work with than AMDs APUs yet offers worse performance? They still had headroom there. I think it's just for TDP, they limit how much power the GPUs can use since the architecture is oriented at mobile.magnimus1 - Friday, October 5, 2012 - link

Would love to hear your take on how Intel's latest and greatest fares against Qualcomm's latest and greatest!cosmotic - Friday, October 5, 2012 - link

Ah, an MPEG2 encoder. Just in time!jamyryals - Friday, October 5, 2012 - link

This made me :)name99 - Friday, October 5, 2012 - link

We laugh but one possibility is that Intel hopes to sell Haswell's inside US broadcast equipment.There isn't much broadcast equipment sold, but the costs are massive, and there's no obvious reason not to replace much of that custom hardware with intel chips.

And much of the existing broadcast hardware (at least the MPEG2-encoding part) is obviously garbage --- the artifacts I see on broadcast TV are bad even for the prime-time networks, and are truly awful for the budget independent operators.

Much like they have written a cell-tower stack to run on i7's to replace the similarly grossly over-priced custom hardware that lives in cell towers, and are currently deploying in China. Anand wrote about this about two weeks ago.

vt1hun - Friday, October 5, 2012 - link

Do you have an idea when Intel will move to DDR4 ? Not with Haswell according to this article.Thank you

tipoo - Friday, October 5, 2012 - link

Haswell EX for servers will support DDR4, but even Broadwell on desktops is only DDR3, we won't see DDR4 in desktops until 2015.jwcalla - Friday, October 5, 2012 - link

We'll probably see DDR4 in the ARM space before we have it on Intel.Maybe this should be AMD's focus of attack: if they can't compete on performance, at least try on chipset features.

Perhaps Intel's biggest concern would be if somebody comes along with a super-efficient x86 emulator for ARM. Going forward, "legacy applications" is going to be an increasingly important selling point to prevent ARM inroads on the low end.

Microsoft keeping their Windows ARM version locked-down is a key to that too, and likely a deference to their relationship with Intel. But Apple is less likely to similarly constrain themselves.

meloz - Saturday, October 6, 2012 - link

>We'll probably see DDR4 in the ARM space before we have it on Intel.>Maybe this should be AMD's focus of attack: if they can't compete on performance, at least try on chipset features.

The problem with DDR4 is likely going to be the price. We all know how the memory industry likes to jack up the prices whenever a new spec comes out. Remember how expensive DDr3 was when it started to replace DDR2?

Some people joke that this transition is the only time they make any money in the RAM business, and considering the low prices of DDR3 you have to wonder.

DDR4 might offer some performance and power advantage on release, but it will likely be more expensive and take time (12-18 months?) to offer a compelling performance / $ advantage over cheap DDR3 variants.

If AMD is trying to position itself as 'value' brand, chaining themselves to DDR4 (before Intel's volume brings down the prices for everyone) could spell their doom.

Kevin G - Friday, October 5, 2012 - link

Intel is set to launch Ivy Bridge EX on a new socket late in 2013 on a new socket. The on-die controller will likely use memory buffering similar to what Nehalem-EX and Westmere-EX use. The buffer chips may initially use DDR3 but this would allow for a trivial migration to DDR4 since the on-die controller doesn't communicate directly with the memory chips.Come to think of it, Intel could migration Nehalem-EX/Westmere-EX to DDR4 with a chipset upgrade. Vendors like HP put the buffer chips and memory slots on a daughter card so only that part would need replacement.