The iPhone 5 Review

by Anand Lal Shimpi, Brian Klug & Vivek Gowri on October 16, 2012 11:33 AM EST- Posted in

- Smartphones

- Apple

- Mobile

- iPhone 5

Apple's Swift: Pipeline Depth & Memory Latency

Section by Anand Shimpi

For the first time since the iPhone's introduction in 2007, Apple is shipping a smartphone with a CPU clock frequency greater than 1GHz. The Cortex A8 in the iPhone 3GS hit 600MHz, while the iPhone 4 took it to 800MHz. With the iPhone 4S, Apple chose to maintain the same 800MHz operating frequency as it moved to dual-Cortex A9s. Staying true to its namesake, Swift runs at a maximum frequency of 1.3GHz as implemented in the iPhone 5's A6 SoC. Note that it's quite likely the 4th generation iPad will implement an even higher clocked version (1.5GHz being an obvious target).

Clock speed alone doesn't tell us everything we need to know about performance. Deeper pipelines can easily boost clock speed but come with steep penalties for mispredicted branches. ARM's Cortex A8 featured a 13 stage pipeline, while the Cortex A9 moved down to only 8 stages while maintining similar clock speeds. Reducing pipeline depth without sacrificing clock speed contributed greatly to the Cortex A9's tangible increase in performance. The Cortex A15 moves to a fairly deep 15 stage pipeline, while Krait is a bit more conservative at 11 stages. Intel's Atom has the deepest pipeline (ironically enough) at 16 stages.

To find out where Swift falls in all of this I wrote two different codepaths. The first featured an easily predictable branch that should almost always be taken. The second codepath featured a fairly unpredictable branch. Branch predictors work by looking at branch history - branches with predictable history should be, well, easy to predict while the opposite is true for branches with a more varied past. This time I measured latency in clocks for the main code loop:

| Branch Prediction Code | ||||||

| Apple A3 (Cortex A8 @ 600MHz | Apple A5 (2 x Cortex A9 @ 800MHz | Apple A6 (2 x Swift @ 1300MHz | ||||

| Easy Branch | 14 clocks | 9 clocks | 12 clocks | |||

| Hard Branch | 70 clocks | 48 clocks | 73 clocks | |||

The hard branch involves more compares and some division (I'm basically branching on odd vs. even values of an incremented variable) so the loop takes much longer to execute, but note the dramatic increase in cycle count between the Cortex A9 and Swift/Cortex A8. If I'm understanding this data correctly it looks like the mispredict penalty for Swift is around 50% longer than for ARM's Cortex A9, and very close to the Cortex A8. Based on this data I would peg Swift's pipeline depth at around 12 stages, very similar to Qualcomm's Krait and just shy of ARM's Cortex A8.

Note that despite the significant increase in pipeline depth Apple appears to have been able to keep IPC, at worst, constant (remember back to our scaled Geekbench scores - Swift never lost to a 1.3GHz Cortex A9). The obvious explanation there is a significant improvement in branch prediction accuracy, which any good chip designer would focus on when increasing pipeline depth like this. Very good work on Apple's part.

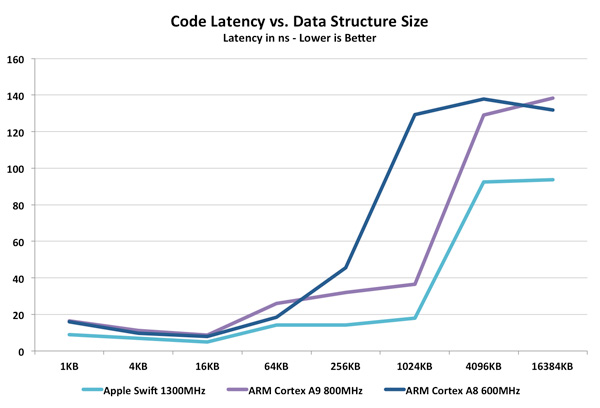

The remaining aspect of Swift that we have yet to quantify is memory latency. From our iPhone 5 performance preview we already know there's a tremendous increase in memory bandwidth to the CPU cores, but as the external memory interface remains at 64-bits wide all of the changes must be internal to the cache and memory controllers. I went back to Nirdhar's iOS test vehicle and wrote some new code, this time to access a large data array whose size I could vary. I created an array of a finite size and added numbers stored in the array. I increased the array size and measured the relationship between array size and code latency. With enough data points I should get a good idea of cache and memory latency for Swift compared to Apple's implementation of the Cortex A8 and A9.

At relatively small data structure sizes Swift appears to be a bit quicker than the Cortex A8/A9, but there's near convergence around 4 - 16KB. Take a look at what happens once we grow beyond the 32KB L1 data cache of these chips. Swift manages around half the latency for running this code as the Cortex A9 (the Cortex A8 has a 256KB L2 cache so its latency shoots up much sooner). Even at very large array sizes Swift's latency is improved substantially. Note that this data is substantiated by all of the other iOS memory benchmarks we've seen. A quick look at Geekbench's memory and stream tests show huge improvements in bandwidth utilization:

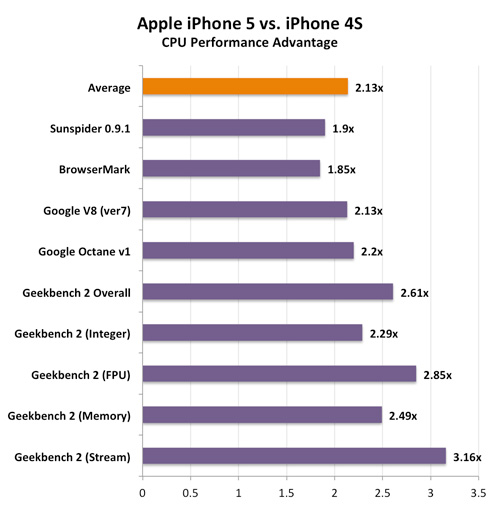

Couple the dedicated load/store port with a much lower latency memory subsystem and you get 2.5 - 3.2x the memory performance of the iPhone 4S. It's the changes to the memory subsystem that really enable Swift's performance.

276 Comments

View All Comments

A5 - Tuesday, October 16, 2012 - link

Double the browsing time while moving to LTE and roughly the same in everything else despite double the performance is pretty impressive.rarson - Thursday, October 18, 2012 - link

I'm pretty sure they mentioned about a million times that "this is the new paradigm blah blah blah, where if you use heavy processing power more often, the battery life will diminish faster" (I'm paraphrasing here). I'm fine with that. The iPhone 5 shows some pretty impressive battery life in light workloads and doesn't actually do all that bad in heavy workloads despite how much number crunching it's doing, even though it might actually tank the battery life down to less-than-4S levels.It's a tradeoff: you get more power or longer battery life, depending on how you use it. The article paints this as a bad thing, but I disagree; it's obviously making much more efficient use of the hardware. Because of that, I definitely think the battery life overall is better, even though sometimes it might be worse. And you're still getting a lot more number crunching for the watts used.

Center - Tuesday, October 16, 2012 - link

In the intro, the screen specs on the iphone 5 is listed as 1136x960.. should be 1136x640.But great article as always, Anandtech!

Krysto - Tuesday, October 16, 2012 - link

I hope we'll see the same kind of thorough review of Samsung's Exynos 5 Dual chip, Anand.ltcommanderdata - Tuesday, October 16, 2012 - link

Isn't TI supposed to become the first shipping Cortex A15 SoC? I expect Anandtech to thoroughly review the first Cortex A15 SoC. There shouldn't be a need to go into the same detail (on the CPU side) for every subsequent one unless preliminary tests show something significantly different.Kidster3001 - Monday, October 22, 2012 - link

Samsung and Qualcomm do not ship generic ARM chips. They purchase licenses to use the ARM instruction set, not the chip design. Their chips are highly customized and perform differently.Using your logic to just review the first A15 class chip and consider the rest to be comparable is similar to just reviewing the first new car to be released every year and assume the rest will be comparable.

btw, TI is getting out of the business. I doubt they will ship first, or ever.

A5 - Tuesday, October 16, 2012 - link

Considering the fact that Krait got several articles here, I'd imagine that whatever the first shipping A15 chip is will get significant coverage.Wurzelsepp - Tuesday, October 16, 2012 - link

Great review, you really have to give Apple credit for building an amazing SoC.It's interesting to see how well the Adreno competes with SGX-543MP3, the new Nexus 4 with this GPU is going to be amazing.

Krysto - Tuesday, October 16, 2012 - link

One thing both the iPhone and the Intel Atom processors will keep lacking for a year from now, will be OpenGL ES 3.0 support. Apple might bring it to the new iPad 4 this spring, but the iPhone won't have it until the next iPhone, in the fall of 2013, obviously. Same with Intel, they won't be supporting it at least until end of 2013.In the meantime both Adreno 320 and Mali T604 are supporting it, and will come out this fall.

darwinosx - Tuesday, October 16, 2012 - link

A year from now and something 'coming out this fall". Right.