MIPS Technologies Updates Processor IP Lineup with Aptiv Series

by Ganesh T S on May 10, 2012 8:55 AM ESTThe proAptiv family of processors can contain 1 to 6 proAptiv cores, each of which implements in about half the size of a standard Cortex-A15 core. This is not entirely impossible, given that some people in the industry feel that ARM's Cortex-A15 implementation takes up too much area for the advertised performance. However, it is likely that the NEON engine is being accounted for in the Cortex-A15 area while the proAptiv implementation doesn't take into account the 32 bit SIMD engine (DSP ASE). [ Update: MIPS clarified that the DSP ASE is not a configurable block and is included in the quoted area. The precise area numbers for ARM are estimates only, since ARM has published no concrete specifications for the Cortex-A15. MIPS also attempted to remove the estimated area for NEON, with the desire to achieve as close to an “apples to apples” comparison in area as possible].

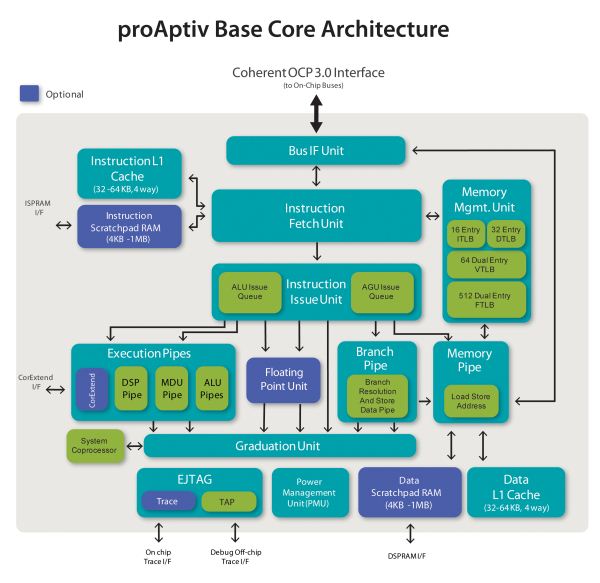

The proAptiv core is a superscalar out-of-order CPU with quad instruction fetch and fused triple dispatch. In the absence of any dependencies, the CPU can issue up to four integer and two floating point operations. Multi-level TLBs and branch target buffers / sophisticated branch prediction aid in getting more than 60% better performance over the previous generation 1074K series. The FPU is dual issue and runs at the same speed as the CPU.

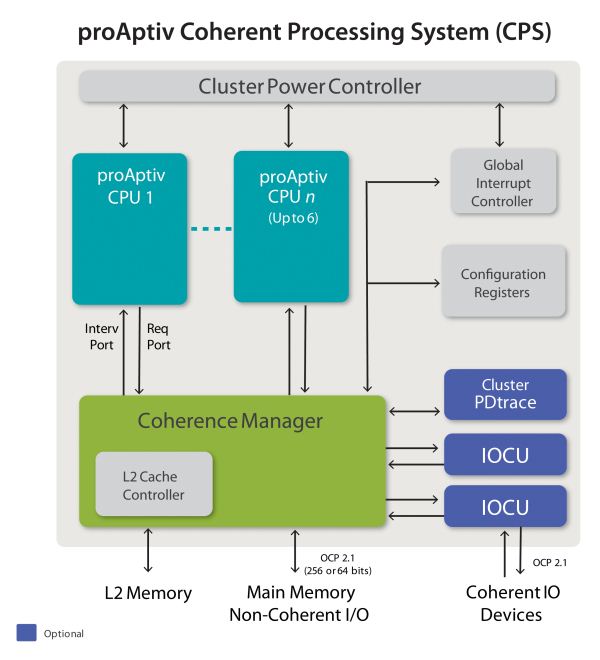

The proAptiv and interAptiv families implement EVA (Extended Virtual Addressing) in order to better utilize the available address space. Similar to the Cortex-A15, the IP includes a coherence manager and an integrated L2 cache controller with ECC support. While Cortex-A15 supports up to 32 cores, the proAptiv family supports up to 6. An interesting aspect of the Coherent Processing System (CPS) is the presence of a cluster power controller which does clock gating per core (common in other multi-core CPUs also) and voltage domain / gating per core. The latter has interesting applications in scenarios similar to ARM's big:LITTLE architecture. Instead of tying up a big core such as the A15 with a smaller one like the A7, MIPS suggests that licensees could implement a multi-core proAptiv system with some cores running at much lower frequencies / lower voltage to save upon power (since the proAptiv cores are already small compared to the A15 core).

| Architecture Comparison | |||||||||

| proAptiv | ARM Cortex A9 | Qualcomm Krait | ARM Cortex A15 | ||||||

| Decode | 3-wide | 2-wide | 3-wide | 3-wide | |||||

| Pipeline Depth | 13 stages | 8 stages | 11 stages | 15 stages | |||||

| Out of Order Execution | Y | Y | Y | Y | |||||

| Pipelined FPU | Y | Y | Y | Y | |||||

| SIMD / Media Processing Engine | DSP ASE (32-bit wide) | Optional MPE (64-bit wide) | Y (128-bit wide) | Optional MPE (128-bit wide) | |||||

| Process Technology | 40nm / 28nm | 40nm / 32nm | 28nm | 28nm | |||||

| Typical Clock Speeds | 1.2GHz* | 1.2GHz | 1.5GHz | 2.5GHz | |||||

While ARM expects the A15 to reach up to 2.5 GHz in the HP/G processes, MIPS only expects up to 1.5 GHz. That said, embedded applications using the proAptiv are likely to be power sensitive, and while peak performance of the A15 is likely to be much better than the proAptiv family, MIPS can tout the smaller size for equivalent performance as an advantage.

*Update: MIPS supplied detailed feedback on our architecture comparison, and I will leave it here for readers to take note:

- MIPS and ARM provide synthesizable IP. As such, these technologies can be implemented in any process geometry and node, with standard cells and memories. At that point, it all comes down to what target a customer shoots for, what physical IP libraries and memories they use, and other implemetation specific aspects.

- MIPS at 1.2 GHz is using readily available using TSMC's 12 track SVt libraries and representing worst case silicon corner results with production margins. MIPS projects that using more aggressive implementation techniques and typical corner silicon, proAptiv implementations can reach 2.0-2.5 GHz (similar to the Cortex-A15) [ Editor's Note: The conditions under which the Cortex -A15 reaches 2.5 GHz are unclear ]

40 Comments

View All Comments

Daniel Egger - Saturday, May 12, 2012 - link

The problem is: Maybe MIPS just woke up but as a matter of fact this market is long gone for them since they don't have the force to push anything around. Intel is a much bigger company trying to achieve the very same thing but they're barely moving forward.Of course one is free to assembly SoCs with MIPS cores but why would one do that? Most of the auxiliary ICs needed for the completely picture are using ARM-optimized or ARM-only interfaces so there're almost no components to choose from while the generic ones (utilizing PCI(e) or USB) use far too much energy and/or space and are usually not synthesizable. Then there is the price issue: MIPS SoCs for mobile devices will be low volume at the beginning and thus quite expensive compared to ARM devices. And then there's the tooling and compatibility issue: The MIPS hardware support for e.g. Android is rather limited and alpha quality in most areas while ARM and even x86 are quite mature. And then there's the market compatibility issue: Good software needs natively compiled code to perform well, ARM is the default here and x86 will bring an ARM emulator to the table; MIPS can't do snitch here...

My prediction: Maybe we will see some insane multi-chip prototypes or even one or two (likely Chinese) SoCs and systems based on that for absolute low end phones but they'll go nowhere in the market.

I'll be far more interesting to see how long it'll take e.g. Ralink to pick up the Aptiv Series for their WLAN SoCs. ;)

Scipio Africanus - Thursday, May 10, 2012 - link

For anyone who is old enough and fortunate enough to remember the SGI workstations, its pretty sad to see what's become of MIPS based machines. My college was an SGI shop and our 6-CPU R4400 SGI Octane server was an awesome sight to behold in the days of Pentium 1 and 2. So were the Indy and Indigo workstations where we would play GLQuake.martinw - Friday, May 11, 2012 - link

Octane was a dual socket workstation, not a 6 socket server. Perhaps you are thinking of a Challenge server?I remember when the first R4k and the first R10k SGI machines came out - amazing performance at the time...

Scipio Africanus - Friday, May 11, 2012 - link

You're right, it was a Challenge L server now that I think about it.During the introduction tour, we saw a real time rendering of a shark. Of course it looked cartoonish by any standard today but the fact that the motion was fluid and it was being rendered real time was jaw dropping. Seeing that and be awestruck is stuck in my memory permanently.

iwod - Thursday, May 10, 2012 - link

1. I am pretty sure MIPS is older then ARM. While the article points to ARM being older.2. Do this news IPs have something similar to big.LITTLE?

3. Performance / Mhz doesn't matter, Performance / Watts does.

4. Apart from MIPS being used in Network equipment, and some set top box, and some Tablet. There are no new market that are using them. Network Market uses them solely because they dont want to reinvest in software and hardware. ( Hence why our Router is still dog slow ).

And I also dont understand why Tablet Maker would want to use MIPS instead. How much cheaper is it?

5. Even NAS moved to ARM based SoC ( Kirkwood ) instead of MIPS many years ago.

6. Set Top Box maker are now moving to wards ARM solution since there are many more ready made solution.

So yea, What exactly does MIPS have an advantage? Unlike Intel who could damn well push Atom into 14nm Node and just Brute Force winning by Manufacturing Technology.

jamyryals - Friday, May 11, 2012 - link

Nice article Ganesh, I learned a lot. Keep up the good work.Avenkidur - Saturday, May 12, 2012 - link

If process technology plateaus, or even slows, and we stop harvesting the benefits of shrinkage, power efficiency, speed, and cost -- could it be an opportunity for MIPS and Micro-Kernels? Technology is at the point where the best design is allocating all resources to the computer to think for itself instead of trying to guess ahead?They both seemed ahead of their time, elegant in theory but challenged to deliver on performance on an open playing field.

ARM is doing well primarily because it is more power efficient than x86 and it crossed the threshold of good enough for smartphones. MIPS is fundamentally even more power efficient than ARM, and it will easier scale to more cores.

I mentioned Micro-Kernels because I feel it is the same design philosophy, just in software. They've got an opportunity coming up to be a single OS that spans a broad range of targeted usages -- they can securely enable and disable drivers on the fly, and the core codebase is not polluted with legacy needs so the whole thing can be secure, while rapidly iterating into new possible features (it's not just sound and video now. Multiple microphones, NFC, motion sensing, computer vision --- who knows what else might be designed in at a deep level.)

iOS is only 5 years old, and you feel it: on what the new devices can't do (fast-switching instead of multi-tasking, that animated lag coverup), on the old devices that can't keep up under the updates that have features bundled in they can't use, the need to restart to update the OS, a software crash can take the whole system down, the multitude of ways to hack into a strangers' phone, the extra work necessary just to port one application to AppleTV, iPod/iPhone, iPad, iMac.

Avenkidur - Saturday, May 12, 2012 - link

duh.. I forgot to mention that Micro-Kernels are the best suited to take advantage of multiple cores, which is the first reason I brought them into a post about it maybe being a chance for MIPS to make a dentxenol - Saturday, May 12, 2012 - link

It's nice to know that ARM isn't going to be the only 32-bit guy in the microcontroller universe once the 8-bit/16-bit guys start phasing out. I just hope others take MIPS in.I also guess that depends on whether or not software development tools for Aptiv are up to snuff.

ET - Monday, May 14, 2012 - link

That's the best article about these processors that I found. I love it that you went to MIPS for clarifications.