The Ivy Bridge Preview: Core i7 3770K Tested

by Anand Lal Shimpi on March 6, 2012 8:16 PM EST- Posted in

- CPUs

- Intel

- Core i7

- Ivy Bridge

Ivy Bridge Architecture Recap

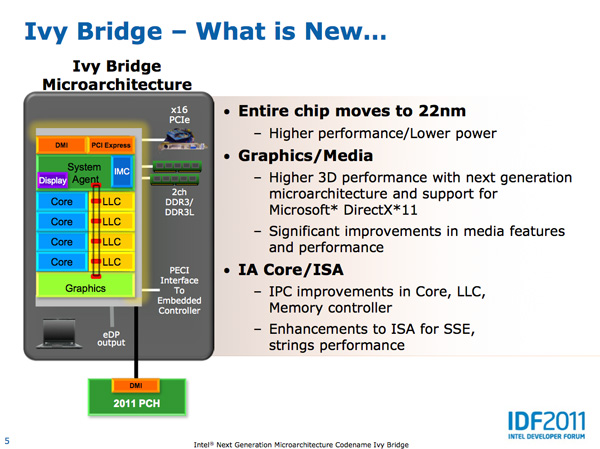

At IDF Intel disclosed much of Ivy's CPU architecture, but below is a quick summary:

- 4-wide front end with µOp cache from Sandy Bridge

- OoO execution engine from Sandy Bridge

- Data structures previously statically shared between threads can now be dynamically shared (e.g. DSB queue), improves single threaded performance

- FP/integer divider delivers 2x throughput compared to Sandy Bridge

- MOV instructions no longer occupy an execution port, potential for improved ILP when MOVs are present

- Power gated DDR3 interface

- DDR3L support

- Max supported DDR3 frequency is now 2800MHz (up from 2133MHz), memory speed can be moved in 200MHz increments

- Lower system agent voltage options, lower voltages at intermediate turbo frequencies, power aware interrupt routing

- Power efficiency improvements related to 22nm

- Configurable TDP

I've highlighted the three big items from a CPU performance standpoint. Much of the gains you'll see will come from those areas coupled with more aggressive turbo frequencies.

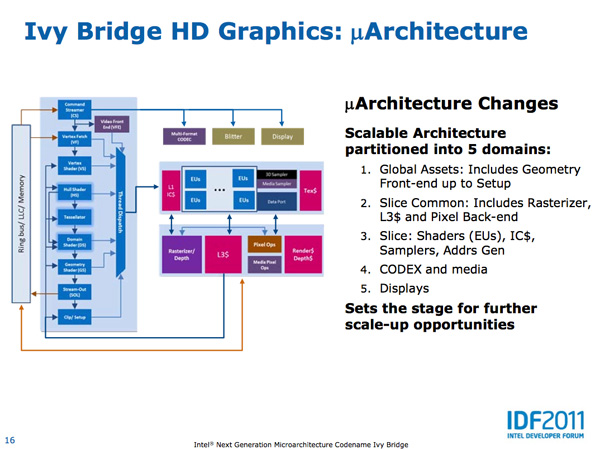

On the GPU, the improvements are more significant. Some of the major changes are below:

- DirectX 11 Support

- More execution units (16 vs 12) for GT2 graphics (Intel HD 4000)

- 2x MADs per clock

- EUs can now co-issue more operations

- GPU specific on-die L3 cache

- Faster QuickSync performance

- Lower power consumption due to 22nm

195 Comments

View All Comments

silverblue - Wednesday, March 7, 2012 - link

At the very least, AMD need a less power hungry successor to Bulldozer. From the Xeon review, it's mentioned that they should be in a position to do this, and could at least clock the thing a lot higher and still use less power than Bulldozer. Regardless, that IPC deficit is a killer - the following page is so telling of the architecture's current limitations:http://www.anandtech.com/show/4955/the-bulldozer-r...

abianand2 - Wednesday, March 7, 2012 - link

1. General curiosity: You stated you did not get a sanction or support from Intel for this preview. I believed that sort of a thing isn't allowed before the release date. How do exceptions like this work?2. Specific: I observed most of the discrete GPU tests were at 1680x1050, where there . Any reason for this? I guess it is since this is just a preview. Am I right? Any other reason?

Thanks

Kjella - Wednesday, March 7, 2012 - link

1. If you want to officially review the chip, you sign an NDA and Intel provides you with it. Here he got access to it from a partner, who probably broke their agreements but Anand never signed any agreement so he can publish whatever he wants.2. I would think so ,and in GPU bound scenarios I wouldn't expect much change at all.

InsaneScientist - Wednesday, March 7, 2012 - link

1) Generally what happens with previews and first looks is that the company producing a product (Intel) will send out press samples to reviewers if the reviewers will sign a Non Disclosure Agreement (NDA). When the NDA expires (generally the same time for everyone), the reviewers can post their findings to the public.This is done (I assume) to give reviewers enough time to thoroughly review a product without having (theoretically) to worry about having information leak until the company wants it to get out.

If, on the other hand, a reviewer acquires a product via other means so there is no NDA that they have to sign in order to get the product... well, they're not under NDA, so they're free to disclose whatever they want.

sld - Wednesday, March 7, 2012 - link

What a troll.Start crying when Intel is able to jack up prices by 2x - 3x when AMD is gone.

You don't even realise that his fears of a tock- means that since Ivy Bridge has more features, presumably pushed forward from Haswell, Haswell itself will bring less features to the table.

Hrel - Wednesday, March 7, 2012 - link

WHY!!!!? Does Intel HAVE to disable Hyper Threading on the sub 300 dollar CPU's? It's not like having in ENABLED costs them anything more at all. It would just be providing their customers with a better product. This shit is infuriating. It's there on the chip no matter what, HT should just be on every single Intel chip no matter what. That shit pisses me off SOOOO much.Exodite - Wednesday, March 7, 2012 - link

I would imagine there's going to be a fair few sub-300 USD dual-cores with HT down the line, though I suppose you meant specifically for the quads?The reason seem obvious enough for me, if you need the extra performance in applications that stand to gain from HT you'll have to pay for it.

Frankly I don't see the added cost as anything major, considering the gains.

It's just differentiation really.

Sure, we'd all want more stuff cheaper (or for free!) but lacking HT doesn't in any way cripple a chip.

sicofante - Wednesday, March 7, 2012 - link

It's called market segmentation.Hector2 - Wednesday, March 7, 2012 - link

Chill out. You'll pop a blodd vessel. With all that's happening in the world, THAT's what's pissing you off ? LMAOsld - Wednesday, March 7, 2012 - link

Intel's products get cheaper with smaller dies and with competition. Without competition, their dies cost the same to make, but they rob and loot your pockets and make obscene profits off you because your hated AMD no longer exists as an alternative supplier of good chips.