Understanding TLC NAND

by Kristian Vättö on February 23, 2012 1:14 PM EST- Posted in

- Storage

- SSDs

- OCZ

- Indilinx Everest

- TLC

Weaknesses of TLC: One Degree Worse than MLC

In a perfect world, increasing the number of bits per cell sounds like a very easy way to increase capacities while keeping the prices down. So, why not put a thousand bits inside every cell? Unfortunately, there's a downside to storing more bits per cell.

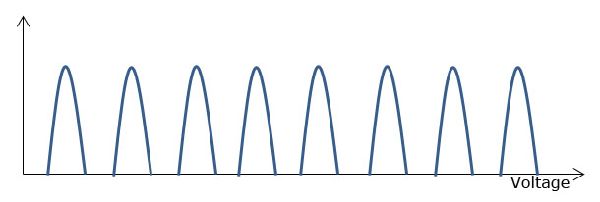

Fundamentally, TLC shares the same problems as MLC when compared to SLC, but takes things one step further. Now that there are eight voltage levels to check, random reads will take more time: 100µs for TLC. That's four times longer than what it takes SLC to random read one bit, and twice as long as what it takes for MLC to complete the same task. Programming will also take longer, but unfortunately we don't have any figures for TLC yet.

| SLC | MLC | TLC | |

| Bits per Cell | 1 | 2 | 3 |

| Random Read | 25 µs | 50 µs | 100 µs |

| Erase | 2ms per block | 2ms per block | ? |

| Programming | 250 µs | 900 µs | ? |

On top of the decrease in performance, TLC also has worse endurance than MLC and SLC. Precise P/E cycle figures are not yet known, but we are most likely looking at around 1000 cycles. Hynix has a brief product sheet for their 48nm TLC flash, which has 2500 P/E cycles. At least in MLC flash, the move to 3Xnm halved the P/E cycles so we would be looking at 1250 cycles. 2Xnm brought even fewer cycles, roughly 3,000, and with same math we get 750 cycles for 2Xnm TLC. X-bit labs reported 1,000 cycles for TLC, which sounds fair. It's also good to keep in mind that endurance can vary depending on the manufacturer and maturity of the process. For example the first 25nm NANDs were good for only ~1,000 cycles, whereas today's chips should last for over 3,000 cycles.

| 5Xnm | 3Xnm | 2Xnm | |

| SLC | 100,000 |

100,000 |

N/A |

| MLC | 10,000 | 5,000 | 3,000 |

| TLC | 2,500 | 1,250 |

750 |

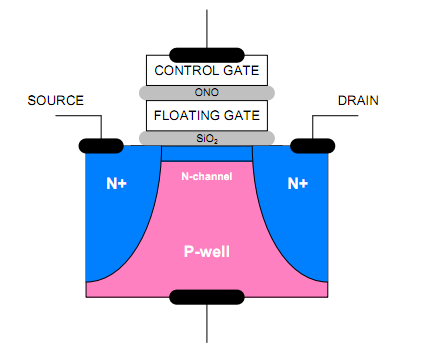

But why does NAND with more bits degrade quicker? The reason lies in the physics of silicon. To understand this, we need to take a look at our beloved Mr. N-channel MOSFET again.

When you program a cell, you are placing a voltage on the control gate, while source and drain regions are held at 0V. The voltage forms an electric field, which allows electrons to tunnel through the silicon oxide barrier from the N-channel to the floating gate. This process is called tunneling. The silicon oxide acts as an insulator and will not allow electrons to enter or escape the floating gate unless an electrical field is formed. To erase a cell, you apply voltage on the silicon substrate (P-well in the picture) and keep control gate voltage at zero. An electric field will be formed which allows the electrons to get through the silicon oxide barrier. This is why NAND flash needs to be erased before it can be re-programmed: you need to get rid of the old electrons (i.e. old data) before you can apply new electrons (i.e. new data).

But what does this have to do with SLC, MLC and TLC? The actual MOSFET is exactly the same in all three cases, but take a look at the table below.

| SLC | "0" | High Voltage |

| "1" | Low Voltage | |

| MLC | "00" | High Voltage |

| "01" | Med-High Voltage | |

| "10" | Med-Low Voltage | |

| "11" | Low Voltage | |

| TLC | "000" | Highest Voltage |

| "001" | High Voltage | |

| "010" | Med-High Voltage | |

| "100" | High-Medium Voltage | |

| "011" | Low-Medium Voltage | |

| "101" | Med-Low Voltage | |

| "110" | Low Voltage | |

| "111" | Lowest Voltage |

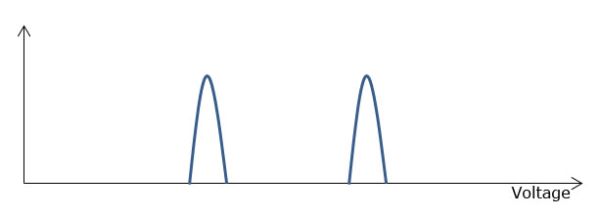

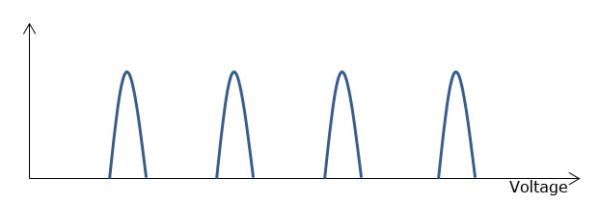

SLC only has two program states, "0" and "1". Hence either a high or low voltage is required. When the amount of bits goes up, you need more voltage stages. With MLC, there are four states, and eight states with TLC. The problem is that the silicon oxide layer is only about 10nm thick and it's not immortal; it wears out every time it's used in the tunneling process. When the silicon oxide layer wears out, the atomic bonds break and during the tunneling process, some electrons may get trapped inside the silicon oxide. This builds up negative charge in the silicon oxide, which negates some of the the control gate voltage.

At first, erasing becomes slower because higher voltages need to be applied (and for a longer time) before the right voltage is found. Higher voltage causes more stress on the oxide, wearing it out even more. Eventually, erasing will take so long that the block has to be retired to maintain the performance. There is a side effect, though. Programming will be faster because there is already some voltage in the cell due to the electron trapping. However, the time won because of that is much smaller than the time it takes to erase the cell when more voltage pulses are required to erase the cell. That's why the block has to be retired when the wear level reaches a certain point.

Here comes the differerence between SLC, MLC and TLC. The fewer bits you have per cell, the more voltage room you have. In other words, SLC can tolerate more changes in the voltage states because it has only two states. In TLC, there are eight, so the margin for errors is a lot smaller.

Lets assume that we have an SLC NAND that takes voltage between 0V and 14V. To program the cell to "1", a voltage between 4V and 5V needs to be applied. Likewise, you need a voltage from 9V to 10V to program the cell to "0". In this scenario, there is 4V of "spare" voltage between the states. If we apply this example to MLC NAND, the spare voltage will be cut to half, 2V. With TLC, that spare value is only 0.67V if we use the same 1V per voltage state ideaology.

However, when the oxide wears out and a higher voltage is needed, the programming voltages go up. To use the SLC example above, you would now need a voltage between 4V and 6V to program the cell to "0". That means a 1V loss in the spare voltage. And here comes the difference. Since SLC has more spare voltage between the states, it can tolerate a higher voltage change until the erase will be so slow that the block needs to be retired. This is why SLC has a substantially higher P/E cycle count; you can erase and reprogram the cell more times. Likewise, TLC tolerates the least change in voltage states, so it has the lowest amount of P/E cycles.

90 Comments

View All Comments

ionis - Friday, February 24, 2012 - link

Both paragraphs you quoted state that TLC has 8 states."TLC takes that a step further and stores three bits per cell, or eight voltage states (000, 001, 010, 011, 100, 101, 110, and 111)."

"With MLC, there are four states, and eight states with TLC. "

JMC2000 - Friday, February 24, 2012 - link

That is the total number of voltage states per cell, i.e.:1 bpc = 2 voltage states per cell (2^1)

2 bpc = 4 voltage states per cell (2^2)

3 bpc = 8 voltage states per cell (2^3)

The voltage states are what allow each bit to read as 0 or 1. TLC has 8 voltage states to allow intermediary changes in the values of the three bits in each cell: 000, 001, 010, 011, 100, 101, 110 and 111.

ionis - Friday, February 24, 2012 - link

Yes. That's the argument. So it should go 16->32->64. Where is the 48 coming from?P.S. we're running out of space in this thread!

Andunestel - Friday, February 24, 2012 - link

The commenter above explained.It's not double each time. The number of combinations, or voltage states, increases exponentially with the number of binary digits represented.

SLC 1 bit (0,1) = 2 states

MLC 2 bits (00,01,10,11) = 4 states

TLC 3 bits ( 000,001,010,011,110,111) = 6 states

Notice that MLC is 100% > SLC, but TLC is only 50% > MLC?

In other words:

SLC = 16GiB

MLC = SLC x 2 = 32 GiB

TLC = SLC x 3 = 48 GiB

- or -

TLC = MLC x 2.5 = 48GiB

Taracta - Sunday, February 26, 2012 - link

For TLC you have left out 100 and 101 so you would haveTLC 3 bits (000, 001, 010, 011, 100, 101, 110, 111) = 8 STATES!

The information is stored per CELL and the same cell is used for SLC, MLC and TLC. The difference between them is the amount of bits per cell that is all. It is not 1 MLC = 2 SLC or 1 TLC = 3 SLC. It is if cell has:

2 electron states = SLC

4 electron states = MLC

8 electron states = TLC

In binary these states are represented by:

2 states = 1bit

4 states = 2bits

8 states = 3bits

This Guy - Friday, February 24, 2012 - link

Your confusing bits with data. Let's look at this problem in decimals.If you have one symbol between 0 and 9, you can represent any number 0-9.

If you have two symbols, 0-9, you can represent any number between 0-99

If you have 3, you can represent 0-999

BUT you still only have three symbols.

Back to binary, a SLC stores 1bit, MLC 2bits and a TLC 3bits. So if you have 3 SLCs, you have 3 bits and 8 possible states. Exactly the same as one TLC. I'll expand this to make this point clear:

# Cells | # Bits | # Bits | # States

6 SLC = 6x1bit = 6bits = 2^6 states

3 MLC = 3x2bit = 6bits = 2^6 states

2 TLC = 2x3bit = 6bits = 2^6 states

All three configurations can store the same data. So to answer your question, the logical blocks which SLC, MLC and TLC apear to be based on have sixteen cells per block. Hence:

16 SLC = 16 x 1bit = 16 bits

= 2^16 states

16 MLC = 16 x 2bit = 32 bits

= 2^32 states

16 TCL = 16 x 3bit = 48 bits

= 2^48 states

I know this was long and tedious, but if I'm not going to recheck this tread and I wanted to make sure I gave enough information that most people reading this should be able to understand the difference between bits and data.

Taracta - Sunday, February 26, 2012 - link

You do notice that in your decimal example that it is increasing by powers of 10 so why in your binary exapmple it is not increasing by powers of 2?16 SLC = 16 x 2^1 bit = 32bits

16 MLC = 16 x 2^2 bit = 64bits

16 TLC = 16 x 2^3 bit = 128bits

No, your exapmples are incorrect so you just further confused the issue.

KitsuneKnight - Sunday, February 26, 2012 - link

SLC doesn't have two bits, it has one. It's not 2 raised to the blah, it's just blah. Same issue applies to your MLC & TLC examples.SLC can _represent_ two values, 'on' or 'off'. MLC can represent 4 values ('on' or 'off' | 'on' or 'off'). And, likewise, TLC represents 8 values ('on' or 'off' | 'on' or 'off' | 'on' or 'off'). As you might notice, each grouping of 'on' and 'off' is a single bit.

His examples are completely correct.

JMC2000 - Friday, February 24, 2012 - link

(What I would give for an EDIT function)I forgot to add that if you had 8 bits per cell, you would have 256 voltage states (0 or 1 for each bit, plus the different variations of 8 on or off bits), though I will not list all possible combinations, as it would take too much time/room.

Taracta - Sunday, February 26, 2012 - link

I completely agree with you. The whole premise of the article is being based on the incorrect graph while having in places, the correct information in the article. There is a difference between place holders and values. SLC - 1 bit place holder 2 bits stored, MLC - 2 bits place holder 4 bits stored and TLC 3 bit place holder 8 bits stored.