AMD Core Counts and Bulldozer: Preparing for an APU World

by Anand Lal Shimpi on November 30, 2009 12:00 AM EST- Posted in

- CPUs

Last week Johan posted his thoughts from an server/HPC standpoint on AMD's roadmap. Much of my analysis was limited to desktop/mobile, so if you're making million dollar server decisions then his article is better suited for your needs.

He also unveiled a couple of details about AMD's Bulldozer architecture that I thought I'd call out in greater detail. Johan has been working on a CMP vs. SMT article so I'll try to not step on his toes too much here.

It all started about two weeks ago when I got a request from AMD to have a quick conference call about Bulldozer. I get these sorts of calls for one of two reasons. Either:

1) I did something wrong, or

2) Intel did something wrong.

This time it was the former. I hate when it's the former.

It's called a Module

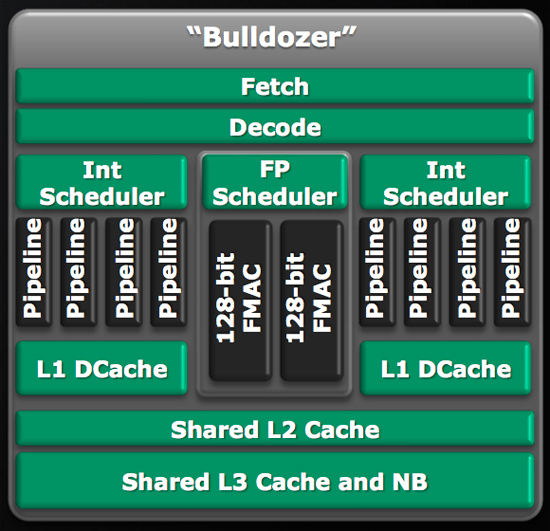

This is the Bulldozer building block, what AMD is calling a Bulldozer Module:

AMD refers to the module as being two tightly coupled cores, which starts the path of confusing terminology. A few of you wondered how AMD was going to be counting cores in the Bulldozer era; I took your question to AMD via email:

Also, just to confirm, when your roadmap refers to 4 bulldozer cores that is four of these cores:

http://images.anandtech.com/reviews/cpu/amd/FAD2009/2/bulldozer.jpg

Or does each one of those cores count as two? I think it's the former but I just wanted to confirm.

AMD responded:

Anand,

Think of each twin Integer core Bulldozer module as a single unit, so correct.

I took that to mean that my assumption was correct and 4 Bulldozer cores meant 4 Bulldozer modules. It turns out there was a miscommunication and I was wrong. Sorry about that :)

Inside the Bulldozer Module

There are two independent integer cores on a single Bulldozer module. Each one has its own L1 instruction and data cache (thanks Johan), as well as scheduling/reordering logic. AMD is also careful to mention that the integer throughput of one of these integer cores is greater than that of the Phenom II's integer units.

Intel's Core architecture uses a unified scheduler fielding all instructions, whether integer or floating point. AMD's architecture uses independent integer and floating point schedulers. While Bulldozer doubles up on the integer schedulers, there's only a single floating point scheduler in the design.

Behind the FP scheduler are two 128-bit wide FMACs. AMD says that each thread dispatched to the core can take one of the 128-bit FMACs or, if one thread is purely integer, the other can use all of the FP execution resources to itself.

AMD believes that 80%+ of all normal server workloads are purely integer operations. On top of that, the additional integer core on each Bulldozer module doesn't cost much die area. If you took a four module (eight core) Bulldozer CPU and stripped out the additional integer core from each module you would end up with a die that was 95% of the size of the original CPU. The combination of the two made AMD's design decision simple.AMD has come back to us with a clarification: the 5% figure was incorrect. AMD is now stating that the additional core in Bulldozer requires approximately an additional 50% die area. That's less than a complete doubling of die size for two cores, but still much more than something like Hyper Threading.

94 Comments

View All Comments

Alouette Radeon - Wednesday, March 10, 2010 - link

How the hell could you embrace Intel after all the harm they've caused AMD, nVidia, VIA and ultimately us, the consumers with their criminal tactics? They don't give a damn about you, they just want your money. A lot of people say that AMD is no different (I know nVidia sure is the same as Intel in that regard) but at least they operate with integrity. They've never been accused of anything underhanded or sneaky. For that matter, neither has VIA. Intel and nVidia on the other hand, while nVidia has never done anything downright CRIMINAL, they've still been dishonest as hell. Intel on the other hand, has stooped about as low as you can go. So go ahead, embrace Intel, just like a stupid biatch who won't leave her abusive spouse. She just keeps going back for more and people like me who have brains can only shake our heads and wonder.AmbroseAthan - Monday, November 30, 2009 - link

While I agree Intel has the performance crown now, I can't knock AMD for being the value right now. Picked up an AMD x4 955 BE and Asus motherboard (full ATX/crossfire) for $230 to build my parents a computer with (Newegg combo). Intel can't compete in that price space easily.dilidolo - Monday, November 30, 2009 - link

Intel can't compete in that price range? No, Intel doesn't want to. Manufacturing capacity is limited, if I can sell more higher margin products, why should I go after lower margin segment? Leave that segment to AMD, the more AMD sells in that segment, the more money AMD looses. If Intel wants to compete in that segment, they can easily kill AMD, that's not what Intel wants to do.siuol11 - Tuesday, December 1, 2009 - link

Ah, the ravings of the marginally informed... How the internet loves them!blyndy - Monday, November 30, 2009 - link

I'm very excited about AMD's brand-new design and how it's new ideas translate into performance, however:"The quad-core Zambezi should have roughly 10 - 35% better integer performance than a similarly clocked quad-core Phenom II"

That sounds a bit low, I hope the final comparable CPUs can manage something more like 15 - 40% better integer performance over their PhII counterparts. Then again perhaps that's just because of Intels large performance increases between their recent architectures making us expect more -- they are more the exception than the rule, so 10 - 35 % shouldn't be sneezed at, although that just may not be competitive on their release in 2011.

mczak - Monday, November 30, 2009 - link

Considering that the int cores actually have less execution units (used to be 3 alus (plus shared load/store, but can do two operations per clock), bulldozer only 2 alus (+ load and separate store)) I think 10-35% better integer performance is amazing. More than that would be a miracle imho...Zool - Monday, November 30, 2009 - link

From the previous article "The extra integer core (schedulers, D-cache and pipelines) adds only 5% die space".So the quad core Zambezi (2 modules, 4 integer pipelines)should have roughly 10-35% better integer performance than a similarly clocked quad-core Phenom II. Thats a super boost per transistor count.

nafhan - Monday, November 30, 2009 - link

Based on AMD's re-defining of the word core that's actually a HUGE improvement. A quad core Zambezi has a similar transistor budget as a dual core Phenom II, and a 10-35% performance improvement.In other words, quad core integer performance for dual core price.

psychobriggsy - Tuesday, December 1, 2009 - link

A quad-core Bulldozer has the same transistor budget as a tri-core Phenom II (if they existed natively), yet performs around 20% better than a quad-core.I think that SMT would have provided easier performance pickings (20% for 5% die space). I don't understand why AMD have been avoiding SMT so far. Sure, 80% more performance for 50% die space isn't to be sneezed at, but it's not so easy pickings.

In addition there are more integer resources than in a Phenom II core, and the FPU has two 128-bit FMAs, so each core could be reasonably bigger. In effect it could be that 1 Bulldozer module is the same size as two Phenom II cores - so all you have then is the 10-35% performance increase. I hope this is per-clock...

titan7 - Sunday, December 6, 2009 - link

Perhaps the k7/k8 didn't make sense to add SMT? The p4 was really designed for it and had it enabled in genII. Look how long it took Intel to get SMT into the Pentium Pro/Core/i7.I suspect AMD is designing for SMT right now, but gen1 is just "get to market ASAP because Intel is faster right now" and genII will have SMT enabled.