Rambus in Cell Processors and Intel's Dual Core Announcements

by Anand Lal Shimpi on February 7, 2005 3:09 PM EST- Posted in

- CPUs

Rambus in Cell

Rambus just proudly announced that their XDR memory interface would be used in the elusive Cell processor, being announced today at the International Solid State Circuits Society conference (ISSCC) in San Francisco.

There's not much surprise that Rambus was selected to be involved with the Cell project, given their previous history with Sony and the Playstation 2, as well as their ability to deliver extremely high bandwidth memory devices on very low pincounts. Sony and Toshiba also signed a licensing agreement back at the start of 2003 to work on the Cell project.

For years Rambus has been telling us that they've been working with GPU manufacturers on getting their high-bandwidth designs into future GPU architectures, and their design win with Sony may just be the key to getting XDR on PC graphics cards as well - especially since NVIDIA handled GPU design for the Playstation 3.

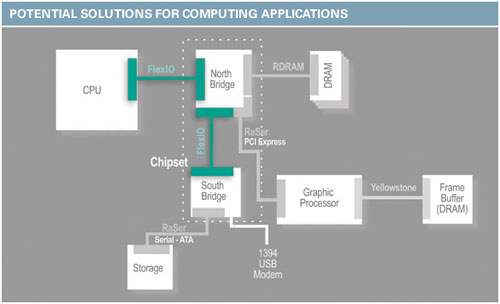

The other interesting part of Rambus' announcement is that they are also responsible for the Cell processor interfaces - it's connection to the outside world (or to other Cell processors). Rambus has had a serial processor bus interface in their IP repertoire for quite some time now, called FlexIO. FlexIO is being used as the processor interface standard for Cell.

FlexIO implements two very important features - what Rambus is calling FlexPhase, and DRSL (Differential Rambus Signaling Level). Normally when traces (wires on a PCB) are laid out, they have to be arranged in such a way that all of the traces going to the same chip have equivalent lengths. As buses get wider and board designs become more complex, trace routing becomes a very serious engineering problem. Because of the need to match trace lengths, you'll often see traces wrapped around themselves or laid out in artificially long paths to make sure that the signals they carry don't arrive sooner than they should. FlexPhase is a technology that allows for on-chip data and clock alignment for signals that don't all arrive at the same time, allowing for traces that aren't matched in length on the PCB. There is an added element of latency introduced by FlexPhase as the chip must handle all clock and data adjustments that are out of phase, but the idea is that what you lose in latency do to FlexPhase, you make up for it in design simplicity, potentially allowing for higher data rates.

The next technology that FlexIO enables is DRSL with LVDS (Low Voltage Differential Signaling), which is a technology similar to what Intel uses in the Pentium 4 to reduce power consumption of their high-speed ALUs. We will actually explain the technology in greater detail later on this week in unrelated coverage, but the basic idea is as follows: normally the lower the voltage you run your interfaces at, the more difficult it becomes to detect an electrical "high" from an electrical "low." The reason being that it is quite easy to tell a 5V signal from a 0V signal, but telling a 0.9V signal from a 0V signal becomes much more difficult. DRSL instead takes the difference between two voltage lines with a very low voltage difference and uses that difference for signaling. By using low signal voltages, you can ensure that even though you may have a high speed bus, power consumption is kept to a minimum. The technology isn't quite sophisticated enough to make the transition to the mobile world, but with some additional circuitry to dynamically enable/disable interface pins it would be quite easy to apply FlexIO to mobile applications of the Cell architecture.

The culmination of these two features is that FlexIO offers up to 8.0GHz data rates based off of a 400 - 800MHz interface clock. It is worth noting that such a high input clock frequency would inherently require some pretty sophisticated technologies to implement.

Because Rambus is providing both the memory and processor I/O interfaces for Cell, it's not too surprising that 90% of the Cell's signaling pins are using Rambus interfaces. Looking at any modern day microprocessor, the biggest use of signaling pins goes to things like enabling multiprocessor support, a chipset interface and a memory interface (obviously varying based on the type of processor we're talking about) - so Rambus' statistics aren't too surprising.

There are still some unanswered questions - mainly whether or not FlexIO will be used to interface with NVIDIA's graphics core (which we're guessing it will) and whether or not XDR will be used for the GPU's local memory (which we're also guessing it will). Given the negative impression of Rambus amongst PC enthusiasts, a successful implementation in PS3 and with NVIDIA's GPU could mean a virtual second chance for Rambus in the PC market.

38 Comments

View All Comments

Viditor - Wednesday, February 9, 2005 - link

"I mean is there ANYONE in the tech world they HAVEN'T sued yet?"Yup...SCO :-)

Desslok - Tuesday, February 8, 2005 - link

How long before RAMBUS starts to sue everyone in this agreement? I mean is there ANYONE in the tech world they HAVEN'T sued yet?Viditor - Tuesday, February 8, 2005 - link

The bottom line is that both AMD and Intel will have multicore, 64bit, and virtualization available across all their lines by the time it's needed for Longhorn. The big question will be performance, and on this I have quite a bit more faith in AMD's offering because they have been designed for it since day 1. That said, I'm looking forward to Intel's next generation after Prescott (probably late 2006), Conroe. Prescott and all of it's derivations have been less than impressive (to say the least), but Conroe will be based on the quite impressive Dothan core.I'm also looking forward to AMD's K10 (also due out in 2006)! 2006 should be a VERY interesting year (especially if MS gets off the dime on Longhorn!).

erikvanvelzen - Tuesday, February 8, 2005 - link

Hmm i forgot the Xeon MP's which are coming. So it's more like 1 Xeon more. But again, the point is clear.erikvanvelzen - Tuesday, February 8, 2005 - link

uhm the sceme i tried to make above doesn't really make sense but yours is even worse.I forgot yonah. maybe i have 1 itanium too much and a xeon. but the point is clear. 11 projects means 11 codenames.

erikvanvelzen - Tuesday, February 8, 2005 - link

I quote:The first thing they sent out to us was an interesting fact - that Intel has 11 multi-core projects that they’re working on for the 2005 - 2006 time period. Doing a quick number check we’re left with the following breakdown:

3 - “Smithfield” based Pentium 4 8xx series CPUs

1 - dual core Pentium 4 Extreme Edition

3 - “Yonah” based Pentium M CPUs (in 2006)

That leaves us with four unaccounted for chips - we’d expect Xeon and Itanium to fill in those blanks nicely.

(end of quote)

Sorry I must disagree with you on that. I think every code name has only ONE project. I think the list is more like this:

DESKTOP (5):

smithfield

presler

conroe (desktop merom)

merom (mobile conroe)

allendale (maybe moved to 2007)

Then we have 4 Xeon products related to the desktop parts and 2 Itanium products (I'm too lazy to look for the code names).

That makes 11!

benk - Tuesday, February 8, 2005 - link

It's a shame that Intel is basically crippling the consumer-level parts compared to the EEs. I wonder if it's to maintain the price premium, or if it has more to do with getting an acceptable yield. I can't imagine that it's a big enough percentage of sales to justify any additional engineer, so I would guess it's the latter.Viditor - Tuesday, February 8, 2005 - link

Jarred - "That is the heart of the whole Rambus problem. The Pentium 3 was not designed AT ALL to make use of Rambus"I disagree somewhat...the real problem that Rambus had was "bang for the buck". They had some good engineering, but the only parts worth anything were the high-clocked ones, and they were WAY overpriced for the boost (if any) you received.

The royalty problem isn't so much that they charge one (as you say, many do), it's that it's so nose-bleedingly high (many times what others charge)! Also, since they are an IP-only company, there can be none of the usual cross-licensing deals which help keep costs down for the manufacturers...

They also have a nasty habit of litigating at the drop of a hat!

JMHO

Viditor - Tuesday, February 8, 2005 - link

Call me cynical (if you must), but I'm reminded strongly of the old 1 GHz race...AMD and Intel came out within a few days of one another (AMD sure snuck THAT one in!), but actually finding shipping chips was another matter (biggest paper launch Intel has ever done IIRC). Of course this time, they are both releasing low demand parts...Opteron and EE (though I think Opteron will have a much greater demand than EE).

It will be interesting to see when the parts are really available this time...

retrospooty - Tuesday, February 8, 2005 - link

Bah... With Rambus, the best thing to do is ignore them... All the specs and hype mean absolutley nothing.Wait until there is a shipping product, and judge it by price and performance. Until then, everything they say or do means nothing.