Rambus in Cell Processors and Intel's Dual Core Announcements

by Anand Lal Shimpi on February 7, 2005 3:09 PM EST- Posted in

- CPUs

Rambus in Cell

Rambus just proudly announced that their XDR memory interface would be used in the elusive Cell processor, being announced today at the International Solid State Circuits Society conference (ISSCC) in San Francisco.

There's not much surprise that Rambus was selected to be involved with the Cell project, given their previous history with Sony and the Playstation 2, as well as their ability to deliver extremely high bandwidth memory devices on very low pincounts. Sony and Toshiba also signed a licensing agreement back at the start of 2003 to work on the Cell project.

For years Rambus has been telling us that they've been working with GPU manufacturers on getting their high-bandwidth designs into future GPU architectures, and their design win with Sony may just be the key to getting XDR on PC graphics cards as well - especially since NVIDIA handled GPU design for the Playstation 3.

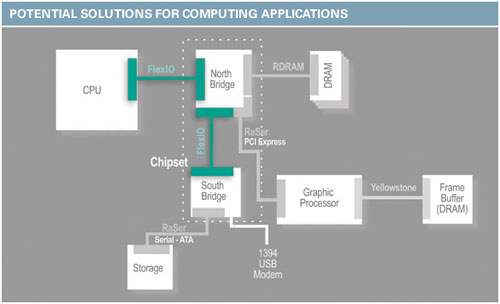

The other interesting part of Rambus' announcement is that they are also responsible for the Cell processor interfaces - it's connection to the outside world (or to other Cell processors). Rambus has had a serial processor bus interface in their IP repertoire for quite some time now, called FlexIO. FlexIO is being used as the processor interface standard for Cell.

FlexIO implements two very important features - what Rambus is calling FlexPhase, and DRSL (Differential Rambus Signaling Level). Normally when traces (wires on a PCB) are laid out, they have to be arranged in such a way that all of the traces going to the same chip have equivalent lengths. As buses get wider and board designs become more complex, trace routing becomes a very serious engineering problem. Because of the need to match trace lengths, you'll often see traces wrapped around themselves or laid out in artificially long paths to make sure that the signals they carry don't arrive sooner than they should. FlexPhase is a technology that allows for on-chip data and clock alignment for signals that don't all arrive at the same time, allowing for traces that aren't matched in length on the PCB. There is an added element of latency introduced by FlexPhase as the chip must handle all clock and data adjustments that are out of phase, but the idea is that what you lose in latency do to FlexPhase, you make up for it in design simplicity, potentially allowing for higher data rates.

The next technology that FlexIO enables is DRSL with LVDS (Low Voltage Differential Signaling), which is a technology similar to what Intel uses in the Pentium 4 to reduce power consumption of their high-speed ALUs. We will actually explain the technology in greater detail later on this week in unrelated coverage, but the basic idea is as follows: normally the lower the voltage you run your interfaces at, the more difficult it becomes to detect an electrical "high" from an electrical "low." The reason being that it is quite easy to tell a 5V signal from a 0V signal, but telling a 0.9V signal from a 0V signal becomes much more difficult. DRSL instead takes the difference between two voltage lines with a very low voltage difference and uses that difference for signaling. By using low signal voltages, you can ensure that even though you may have a high speed bus, power consumption is kept to a minimum. The technology isn't quite sophisticated enough to make the transition to the mobile world, but with some additional circuitry to dynamically enable/disable interface pins it would be quite easy to apply FlexIO to mobile applications of the Cell architecture.

The culmination of these two features is that FlexIO offers up to 8.0GHz data rates based off of a 400 - 800MHz interface clock. It is worth noting that such a high input clock frequency would inherently require some pretty sophisticated technologies to implement.

Because Rambus is providing both the memory and processor I/O interfaces for Cell, it's not too surprising that 90% of the Cell's signaling pins are using Rambus interfaces. Looking at any modern day microprocessor, the biggest use of signaling pins goes to things like enabling multiprocessor support, a chipset interface and a memory interface (obviously varying based on the type of processor we're talking about) - so Rambus' statistics aren't too surprising.

There are still some unanswered questions - mainly whether or not FlexIO will be used to interface with NVIDIA's graphics core (which we're guessing it will) and whether or not XDR will be used for the GPU's local memory (which we're also guessing it will). Given the negative impression of Rambus amongst PC enthusiasts, a successful implementation in PS3 and with NVIDIA's GPU could mean a virtual second chance for Rambus in the PC market.

38 Comments

View All Comments

Ice9 - Thursday, February 10, 2005 - link

#17, first of all, tech companies sue each other all the time.Intel has sued far more companies in its lifetime than Rambus has. Rambus to date has sued what, 5 companies? All for the same patent infringement?

How many companies has Intel or AMD sued over its patents?

Honestly, if you look at how many open patent lawsuits there are for any given technology company, you'll see that Rambus is actually a tame little kitten by comparison. But people love to hate Rambus because they have the better (and more threatening) technology, so it's smear-smear-smear until they hopefully go away.

Well, they aren't. So either embrace the superior technology or let the memory manufacturing cartels tell you that you need the slower stuff that costs more :)

Ice9 - Thursday, February 10, 2005 - link

Rambus is going to be all over the place with Cell. They're using 3 key technologies for Cell, all invented by Rambus.XDR (octal data rate memory), Redwood chip-to-chip internconnects, and Flexphase - which gets around that pesky equal-trace-length limitation that's been dogging DRAM for years.

Thus far, there's simply nothing coming out of the lazy memory manufacturers that make up JEDEC to compete with it. And if they decide to try, they better make sure they steer clear of Rambus patents :)

Oh, and yeah, none of it is vaporware either, at least not on Rambus' side. Toshiba has been sampling XDR for quite some time, and the interconnects have been available for even longer.

All roads still lead to Rambus.

Viditor - Thursday, February 10, 2005 - link

Tujan - "Why leave this out.Hyperthreaded software will remain to those that can pay for the higher priced equipment"Hyperthreading is a way of simulating dual cores without all of the assets to process it. This is beneficial to Intel as they have a problem keeping the pipes fed. However, real dual cores use exactly the same software as HT, but they can process it completely.

Viditor - Thursday, February 10, 2005 - link

March...what retro said is correct.Live - "It looks to me that AMD:s lack of production capacity will really hurt us this year"

I doubt it, though on it's face it might appear so. The missing element is the 90nm ramp...

For example, at 130nm you get 186 candidate 3500+ dice per wafer, and at 90nm you get 329. At the moment, they are only halfway through their ramp and accelerating. Also, we are entering the low demand period...

This might also explain why AMD is delaying most of their desktop dualcore until 2006 (when Fab36 comes on line). 90nm dualcores will be about the same size as their 130nm single core counterparts.

Tujan - Thursday, February 10, 2005 - link

What’s interesting is that the 90nm dual core Pentium 4 Extreme Edition will feature Hyper Threading support, something that is left out of the regular Pentium 4 8xx series. """This is a weird habit of Intels. Leaving a ventured into technology 'out of the next 'great new thing". Software wich was created to take advantage of hyperthreading will no longer be a criteria of software shoppers. No will the work of coders putting their software up to 'spec. be satified of their job well done.

Why leave this out.Hyperthreaded software will remain to those that can pay for the higher priced equipment.Development will remain on those that purchase that equipment.New technology will have another reason to consider themselves 'low end".

- hi ya

Tujan - Thursday, February 10, 2005 - link

retrospooty - Wednesday, February 9, 2005 - link

#20AMD scrapped the K9, and decided to go straight on with the K10 design.

Live - Wednesday, February 9, 2005 - link

It looks to me that AMD:s lack of production capacity will really hurt us this year. The only part that seems able to put up fight against AMD is the ridiculously priced Extreme Editions. On the other hand AMD are already at full capacity and making dual core will only reduce that even more. So Intel faces no real threat. Here in Sweden there has been a shortage of AMD 90 nm for 2 months know so they can’t be making enough to satisfy demand.Hopefully AMD will get the new fab up soon and/or Cell will be as good as can be and we can play with that instead. Intel looks like a nightmare for a value minded costumer.

MarchTheMonth - Wednesday, February 9, 2005 - link

"I'm also looking forward to AMD's K10 (also due out in 2006)!"Considering that AMD has gone by increasing the number scheme by 1, and the current processor core is K8, do you mean K9, or did K10 development jsut look so good that the skipped over K9 and went right to K10? I figure an investor would know...

MarchTheMonth - Wednesday, February 9, 2005 - link

"Yup...SCO :-)"That just totally made my day.