AMD Zen Microarchitecture: Dual Schedulers, Micro-Op Cache and Memory Hierarchy Revealed

by Ian Cutress on August 18, 2016 9:00 AM ESTSimultaneous Multi-Threading

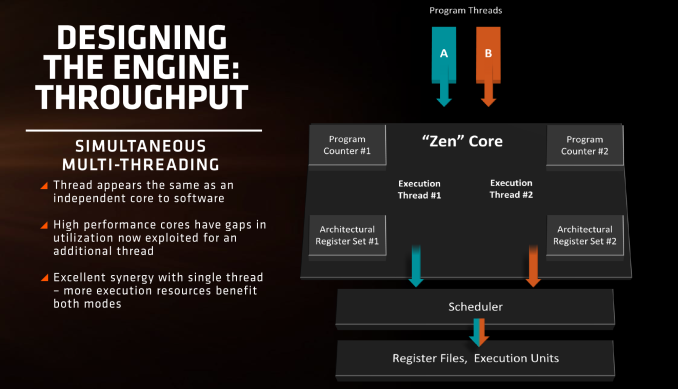

On Zen, each core will be able to support two threads in what is called ‘simulatenous multi-threading’. Intel has supported their version of SMT for a number of years, and other CPU manufacturers like IBM support up to 8 threads per core on their POWER8 platform designs. Building a core to be able to use multiple threads can be tough, as it requires a lot of resources to make sure that the threads do not block each other by consuming all the cache and buffers in play. But AMD will equip Zen with SMT which means we will see 8C/16T parts hitting the market.

Unlike Bulldozer, where having a shared FP unit between two threads was an issue for floating point performance, Zen’s design is more akin to Intel’s in that each thread will appear as an independent core and there is not that resource limitation that BD had. With sufficient resources, SMT will allow the core instructions per clock to improve, however it will be interesting to see what workloads will benefit and which ones will not.

Timeframe and Availability

At the presentation, it was given that Zen will be available in volume in 2017. As the AM4 platform will share a socket with Bristol Ridge, users are likely to see Bristol Ridge systems from AMD’s main OEM partners, like Dell and others, enter the market before separate Zen CPUs will hit the market for DIY builders. It’s a matter of principle that almost no consumer focused semiconductor company releases a product for the sale season, and Q1 features such events as CES, which gives a pretty clear indication of when we can expect to get our hands on one.

It’s worth noting that AMD said that as we get closer to launch, further details will come as well as deeper information about the design. It was also mentioned that the marketing strategy is also currently being determined, such that Zen may not actually be the retail product name for the line of processors (we already have Summit Ridge as the platform codename, but that could change for retail as well).

Wrap Up

AMD has gone much further into their core design than I expected this week. When we were told we had a briefing, and there were 200-odd press and analysts in the room, I was expecting to hear some high level puff about the brand and a reiteration of their commitment to the high end. To actually get some slides detailing parts of the microarchitecture, even at a basic cache level, was quite surprising and it somewhat means that AMD might have stolen the show with the news this week.

We’ve got another couple of pieces detailing some of the AMD internal/live benchmark numbers during the presentation, as well as the dual socket server platform, the 32-core Naples server CPU, and what we saw at the event in terms of motherboard design.

216 Comments

View All Comments

jamyryals - Monday, August 22, 2016 - link

Excited to see if they execute, I'm rooting for AMD. After two straight Intel chips, I'd love to spend money with AMD again.slyronit - Tuesday, August 23, 2016 - link

I would be happy to see AMD succeed and be relevant in the desktop/tablet/laptop space again. I have stuck with AMD over the years because of the low price to performance ratio and good multithread performance (I use photo editing apps which multithread well) and because Intel is a mis-leading, monopolistic company.soulLover - Thursday, August 25, 2016 - link

no avx2 ? After excluding the Micro-OP cache, the four instruction per cycle are to feed 2 x 128 bit, right ? i.e. 4 x 64 bits / cycle. If I'm not wrong AMD is lacking serious parallelism in SIMD than Intel AVX2.unimatrix725 - Sunday, August 28, 2016 - link

I have read both In depth Zen reviews, however something huge is missing! No one or any tech site that I'm aware of has went in depth about Global Memory Interface. The best I got out of it was a variant of a PPC on Wikipedia? There needs to be coverage of this. I believe it critical to Zen & AM4 in general. Since there is no more NB&ORSB. Shocked not even Wikipedia has an article. A double edge sword more or less...patrickjchase - Sunday, August 28, 2016 - link

The comment that "some put [a micro-op cache] as a major stepping stone for Conroe" is wrong on a couple levels:First, Conroe didn't have a uop cache. Like many other micro-architectures before and since it could use its uop queue to buffer small loops, but had no uop cache as such.

Second, Intel cores had uop caches long before Conroe. The first Intel x86 microarchitecture with a first-level I-cache that stored decoded uops was Pentium-4. The oft-maligned trace cache was in fact a uop cache. The fact that it went a step beyond and stored superblocks of decoded uops doesn't change the fact that it was a uop cache.

The uop caches first appeared in the "non-Pentium-4" Intel x86 line in Sandy Bridge, two full tocks after Conroe.

Hixbot - Friday, September 2, 2016 - link

Any chance Zen competition will push Intel to release an 8-core mainstream CPU for about $300?